因为专业

所以领先

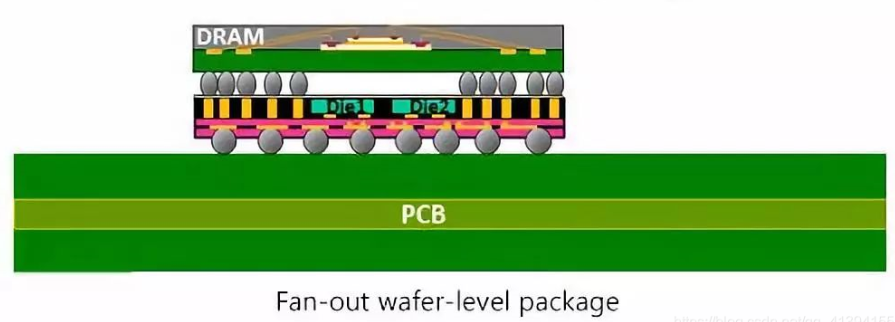

2016 年, 台积电(TSMC)经过在先进封装技术上 近十年的布局和技术沉淀, 在 FOWLP 领域开发了集 成扇出型(Integrated Fan-out, InFO)封装技术[ , 并 成功应用于苹果 iPhone7 系列手机的 A10 应用处理器 , 之后苹果每一代手机应用处理器都采用台积电 的集成扇出型封装技术, 帮助台积电拿下苹果处理器 芯片制造和封装订单。

在先进封装领域, AMD 公司将多项先进封装技术 投入商用。Chiplet, 中文译名芯粒或晶粒, 是近期集 成电路业界的热点话题, Chiplet 是指预先制造好、 具 有特定功能、 可组合集成的晶片, 该技术可以缩小单 颗芯片面积, 提高良品率, 有助于企业控制生产成本 和提高迭代速度。如何实现多芯粒之间的高速互联是 实现 Chiplet 的技术难点, 而 FOWLP 技术的高密度重 布线工艺满足多芯粒之间高速互联的需求。FOWLP 技 术的发展是 Chiplet 技术走向商用的先决条件。AMD 公司在扇出型封装技术上投入巨资, 并且在商业竞争 中率先使用先进的 FOWLP 技术, 该技术路线帮助 AMD 公司在 CPU 和 GPU 领域追赶行业先驱 Intel 和 NVIDIA。在 2019 年发布的 7 nm Zen2 架构锐龙处理器 中, AMD 公司将 CPU 芯片拆分成 CCD 和 cIOD 两部分, 其中仅有负责逻辑运算的 CCD 使用台积电 7 nm 工艺, 对性能要求较低的 cIOD 部分使用了 12 nm 工 艺。Zen2 架构意义重大, 实现了对同期 Intel 产品的性 能追赶, 为提升 AMD 在德国等多国 CPU 市场占有率 奠定了基础。

在 CPU 领域通过先进封装技术取得优势的 AMD 公司也试图将 FOWLP 技术引入到 GPU 领域, AMD 公司于 2022 年 12 月 13 日向市场推出了使用 RDNA 3 架构的 Radeon 7900XTX 显卡, AMD 将显卡核心 Big Navi 3x 拆分为一个 GCD 和六个 MCD, 与 AMD 在 Zen 架构的做法相同, 负责逻辑计算的 GCD 使用了台 积电 5 nm 工艺, 面积为 300 mm 2 , MCD 使用了台积 电 6 nm 工艺, 单颗面积为 37 mm2 。得益于更小的芯 片带来更高的良率, 以及 MCD 芯片成熟工艺, 使得 AMD 的 Big Navi 3x 核心在性能对标竞争厂家 NVIDIA 的 AD102 核心的同时实现了较好的成本控制。

Intel 公 司 结 合 自 身 在 基 板 领 域 的 积 累, 推 出 EMIB(Embedded Multi-Die Interconnect Bridge), 中文 译名为嵌入式多核心互联桥接。EMIB 工艺建立在标 准封装构造流程的基础上, 附加了创建 EMIB 腔的步 骤。连接桥位于空腔中, 并用粘合剂固定在适当的位 置。添加介电层和金属堆积层, 然后进行通孔钻孔和 电镀。作为 CPU 行业的巨头, Intel 公司正试图参与 GPU 市场竞争。在 2022 年 8 月的半导体行业会议 Hot Chips 34 上, Intel 公司公开了一套名为 Ponte Vecchio 的服务器 GPU 架构。Intel 公司作为 GPU 行业的后来 者, 在最新推出的 GPU 产品中使用了比 AMD 公司更 先进的封装技术。Intel 公司称 Ponte Vecchio 内部同时 混用 Intel 7 和台积电 N7 / N5 等多个工艺节点, 并使用 了多达 11 处的 EMIB 结构以实现内部高速互联。

在超算领域, 特斯拉于 2021 年公布了 Dojo 芯片 的概念图, Dojo 是神经网络训练优化超级计算机芯 片, 该芯片将首次使用台积电 InFO_ SoW (System-on -Wafer)技术 , Dojo 使用 6 层 RDL, 将整块 12 英寸 重构晶圆安装在散热盘上, 散热盘可以为芯片提供刚 度并将散热能力从 7000 W 提升至 15000 W。2022 年, FOWLP 技术在 GPU 领域得到了快速的 推广应用, 2021 年底到 2022 年初, 马斯克在推特上 发布多篇推文公布特斯拉自研超算 GPU 芯片, 以取代 特斯拉采购的 NVIDIA 芯片。

2022 年 8 月 Intel 公布全 新服 务 器 GPU 架 构, 12 月 AMD 发 售 消 费 级 GPU7900XTX, 这三家公司为了追赶行业先进水平, 使用的先 进 封 装 技 术 越 发 激 进, 但 市 占 率 最 高 的 NVIDIA 公司仍采用了较保守的封装方案。无论是 CPU、 GPU 还是其他集成电路产业, 均呈现出越是行 业后发者, 使用的封装技术越先进的趋势。如图 2 所 示, 这一趋势在市场规模最大、 竞争最激烈的 GPU 市 场表现尤为明显。并且, 各公司发展先进封装技术的 战略也取得了不错的效果, NVIDIA 公司各类 GPU 产 品线均受到巨大挑战。观察这种趋势对国内半导体行 业的发展很有参考价值, 促进 FOWLP 等先进封装技 术的发展和应用对于试图参与 GPU 市场竞争的集成电 路企业是很有意义的。

在宇航领域, NASA 在 2015 年公布的封装技术路 线图 中 将 2. 5D/ 3D - TSV 技 术 纳 入 封 装 技 术 路 线, 2018 年启动对 2. 5D 封装产品的考核方案和路线图。在美国国家航空航天局电子零件和包装计划(National Aeronautics and Space Administration Electronic Parts and Packaging, NEPP)的赞助下, 美国加州理工学院喷气 动 力 实 验 室 ( California Institute of Technology Jet Propulsion Laboratory, JPL) 的 Ghaffarian 通过一系列 的可靠性实验系统论证了 2. 5D 封装产品的可靠性, 他认为 FOWLP 产品拥有更小的体积重量、 更大的逻 辑运算和存储能力, 而且其可靠性鉴定结果足以满足 NASA 对空间飞行器电子元器件的可靠性要求, 并希 望他的研究成果可以促进 NASA 对 FOWLP 等先进封 装技术的使用。

我国半导体封装企业也在 FOWLP 领域取得了一 系列创新成果。硅基扇出型晶圆级封装 ( Embedded Silicon Fan-out, eSiFO) 是 2015 年由华天科技于大全 教授提出。硅基扇出型封装这一技术路线相比于树脂 扇出型封装, 具有成本低、 翘曲小、 布线密度高、 散 热良好和制程简单等优势, 更容易实现大芯片系统集 成。该工艺被使用于电源管理芯片、 射频收发器芯片、基带处理器和高端网络系统等多种应用领域,

厦门云天半导体开发了 eGFO 嵌入式玻璃封装技 术。玻璃绝缘性好, 高温下不易膨胀, 透光性强, 适 合高频的射频应用和光电应用。玻璃上可以直接做光 路, 满足光电共封装的需求, 光电射频领域也是云天 eGFO 技术的主要应用领域。但是玻璃具有易开裂的 特性, 在玻璃上开孔和挖出嵌埋区域工艺难度高、 效 率低。产品良率是目前制约厦门云天使用玻璃作为载 体的最大因素。

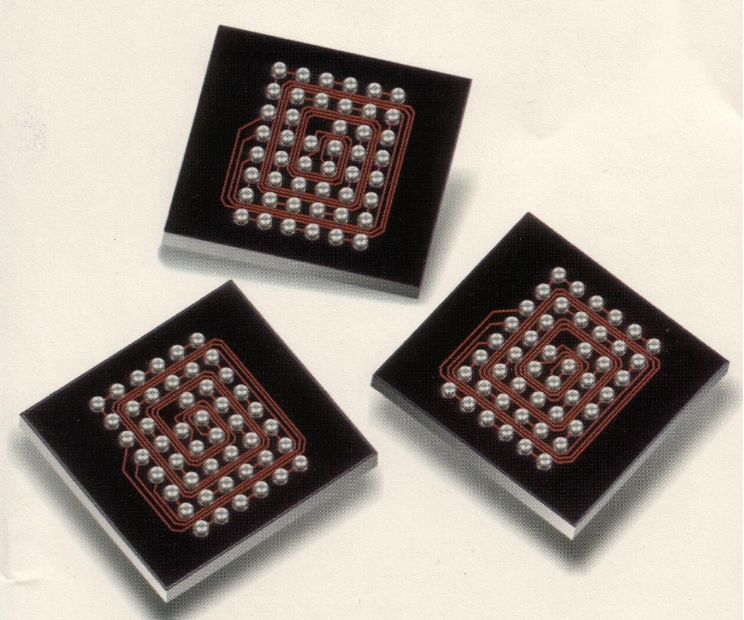

中电五十八所的晶圆级封装工艺平台是目前国内先进、 自主可控的高可靠 12 英寸(兼容 8 英寸) 晶圆级制造加工线, 同时也是国防科技工业认可的信息处 理微系统加工制造平台。自 2017 年通线以来, 平台已 经具备高可靠 12 英寸的晶圆级再布线制备、 晶圆级凸 点制备、 圆片重构等多项晶圆级扇出型集成技术。部 分工艺技术能力(晶圆级封装尺寸、 凸点直径等)达到国际领先水平。同时具备有铅低辐射凸点(Bump) 制 备、 单芯片批量化凸点生长以及可重构三维封装等特 色服务, 可满足军用及宇航长寿命使用要求, 已先后 为国内多家用户单位提供了 GNC 飞行控制、 AD/ DA 集成、 信号截取处理模块等数字信息处理微系统产品 的加工服务, 满足了相关微系统产品小型化、 高性能、 高可靠的应用需求。

航天 772 所通过近几年技术攻关和自主研发, 已 初步具备 小 尺 寸 多 芯 粒 硅 基 集 成 技 术 能 力。针 对 Chiplet 芯粒集成多级互连要求, 面向 40 μm 以下超微 凸点键合, 突破面阵列固态互连等关键技术, 实现了 低温焊接、 高温服役的全流程稳定工艺; 并采用耐湿 “内防护” 结构以及改性耐高温材料, 实现了节距小 于 100 μm, 凸点数大于 10000 个的均匀沉积和致密防 渗集成工艺。

通富微电 2021 年披露其在高性能计算领域建成了 国内顶级 2. 5D/ 3D 封装平台 ( VISions) 及超大尺寸 FCBGA 研发平台, 且完成了高层数再布线技术的开 发, 具备大规模生产 Chiplet 封装能力, 目前在 CPU、 GPU、 服务器领域 5 nm 即将量产。其 Fan-out 技术已 经达到世界先进水平, 高密度扇出型封装平台完成 6 层 RDL 开发。

XDFOI 是长电科技 2021 年推出全系列极高密度 扇出型封装解决方案, 并于 2022 年下半年量产。该封 装解决方案是新型无硅通孔晶圆级极高密度封装技术, 相较于 2. 5D 硅通孔(TSV) 封装技术, 具备更高性能、 更高可靠性以及更低成本等特性。该解决方案在线宽 或线距达到 2 μm 的同时, 可实现多层布线层, 另外, 采用了极窄节距凸块互联技术, 封装尺寸大可集成多 颗芯片、 高带宽内存和无源器件。XDFOI 主要集中于 对集成度和算力有较高要求的 FPGA、 CPU、 GPU、 AI 和 5G 网络芯片等应用产品提供小芯片 (Chiplet) 和异 质封装 (HiP) 的系统封装解决方案。 2022 年 7 月 22 日, 长电科技发文称, 公司在先进封测技术领域取得 新的突破, 实现 4 nm 工艺制程手机芯片的封装以及 CPU、 GPU 和射频芯片的集成封装。

我国 FOWLP 技术与国外先进水平相比差距较小, 且各企业均有自身的特色技术, 但在高密度重布线和 超大面积扇出型封装技术等领域尚有差距。

先进芯片封装清洗:

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

上一篇:有铅助焊剂与无铅助焊剂的区别

![[x]](/template/default/picture/closeimgfz1.svg)