因为专业

所以领先

近些年,先进封装已经成为半导体中越来越普遍的主题,那么半导体先进封装是什么?首先要知道半导体封装是指将生产加工后的晶圆进行切割、焊线、塑封,使电路与外部器件实现连接,并为半导体产品提供机械保护,使其免受物理、化学等环境因素损失的工艺。

随着先进制程工艺逐渐逼近物理极限,包括台积电在内的厂商已经开始将研发方向由先前的“如何把芯片变得更小”转变为“如何把芯片封得更小”,先进封装逐渐成为行业发展重点。

目前半导体封装技术正在从传统封装(SOT、QFN、BGA等)向先进封装(FC、FIWLP、FOWLP、TSV、SIP等)转型。先进封装作为提高连接密度、提高系统集成度与小型化的重要方法,在单芯片向更高端制程推进难度大增时,担负起延续摩尔定律的重任。

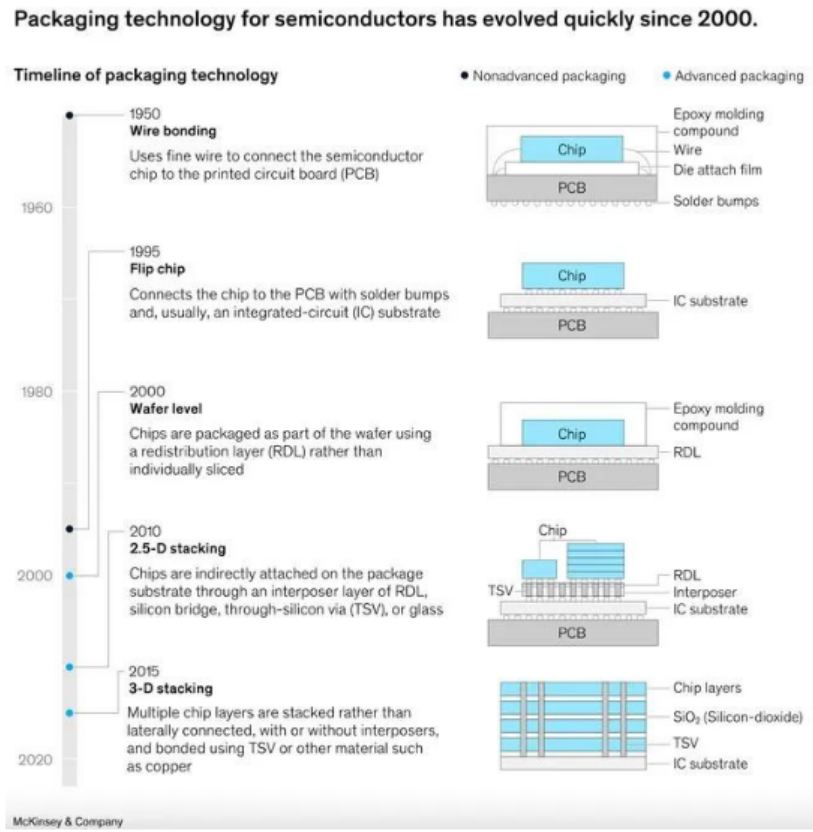

自20世纪90年代中期之后,集成电路封装体的外观(形状、引脚样式)并未发生重大变化,但其内部结构发生了三次重大技术革新:引线键合(Wire Bonding)、倒装封(Flip Chip)和晶圆级封装(WLCSP,Wafer Level Chip Scale Package)。

封装技术的发展史是芯片性能不断提高、系统不断小型化的历史。根据《中国半导体封装业的发展》,半导体封装技术的发展历史可大致分为以下五个阶段:

第一阶段:20 世纪 70 年代以前(通孔插装时代),封装技术是以 DIP 为代表的针脚插装,特点是插孔安装到 PCB 板上。这种技术密度、频率难以提高,无法满足高效自动化生产的要求。

第二阶段:20 世纪 80 年代以后(表面贴装时代),用引线替代第一阶段的针脚,并贴装到PCB 板上,以 SOP 和 QFP 为代表。这种技术封装密度有所提高,体积有所减少。

第三阶段:20 世纪 90 年代以后(面积阵列封装时代),该阶段出现了 BGA、CSP、WLP为代表的先进封装技术,第二阶段的引线被取消。这种技术在缩减体积的同时提高了系统性能。

第四阶段:20 世纪末以后,多芯片组件、三维封装、系统级封装开始出现。

第五阶段:21 世纪以来,主要是系统级单芯片封装(SoC)、微机电机械系统封装(MEMS)。

图片来自于国金证券

半导体先进封装的两个方向:

1、小型化:3D封装突破传统的平面封装的概念,通过单个封装体内多次堆叠,实现了存储容量的倍增,进而提高芯片面积与封装面积的比值。

2、高集成:系统级封装SiP能将数字和非数字功能、硅和非硅材料、CMOS和非CMOS电路以及光电、MEMS、生物芯片等器件集成在一个封装内,在不单纯依赖半导体工艺缩小的情况下,提高集成度,以实现终端电子产品的轻薄短小、低功耗等功能,同时降低厂商成本。

Chiplets——小芯片!目前也是各大厂商研发重点,将大筹码分成许多小筹码。同样是高集成的解决方案。

AMD 是这方面最受欢迎的例子,但这是整个行业的趋势。AMD 可以设计 3 个芯片,一个CPU 核心小芯片和2 个 IO 芯片。这 3 种设计覆盖了很大一部分市场。同时,英特尔设计了 2 个 Alder Lake 台式机芯片和 3 个 Ice Lake 服务器芯片,以服务于相同的潜在市场。因此,AMD 可以节省设计成本,制造比英特尔更多内核的 CPU,并节省收益成本。

小芯片(Chiplet)很棒,但它不是孤立的解决方案。也会遇到许多问题。每个晶体管的成本仍在上升,设计成本飙升,由于需要更多 IO 来与其他芯片接口,小芯片被pad限制。由于 IO 限制,部分芯片无法拆分,因此芯片尺寸仍在达到峰值。

那么行业解决办法是什么?

先进封装!

这就是我们要注意的地方,一些工具供应商将所有倒装芯片封装称为“先进封装”。SemiAnalysis 和大多数业内下游人士不会这么说。因此,我们将所有凸点尺寸小于100 微米的封装称为“先进”。

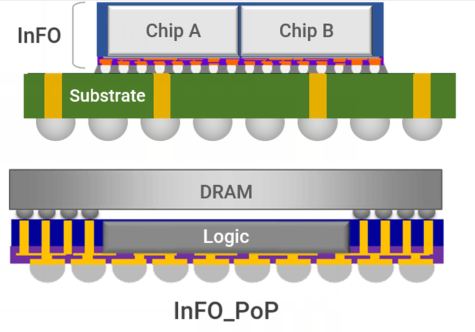

最常见的先进封装类别称为扇出。有些人会争辩说它甚至不是先进的封装,但那些人大错特错。以Apple 为例,他们将让台积电采用应用处理器芯片,并将其与 90 微米到 60 微米数量级的更密集凸块封装到重组或载体晶圆/面板上。与传统倒装芯片封装相比,凸点密度大约高出 8 倍。

这种重组或载体晶圆/面板然后进一步展开 IO,因此得名扇出。然后将扇出封装连接到主板。硅芯片的设计可以减少对pad受限的担忧,因为扇出处的pad较小。该封装还可以封装 DRAM 内存、NAND 存储和PMIC。集成扇出不仅有利于密度,而且它们还在封装上保留了大量的芯片间 IO。否则,该 IO 将不得不以更大的IO 间距尺寸通过主板进行接口。

集成扇出对于高性能应用程序变得越来越普遍,不仅仅是移动应用程序。增长最快的用例是在十多年来设计一直受到限制的事物的网络方面。AMD 将在其服务器 CPU 和 GPU中非常积极地采用扇出。Tesla Dojo 1是集成扇出封装的另一个引人注目的例子,但在晶圆级。SemiAnalysis透露,特斯拉将在发布公告前使用这种包装类型。

在先进封装中,有 2.5D 和 3D 封装。2.5D 涉及封装在其他硅片上的硅片,但较低的硅片专用于布线,没有有源晶体管。这通常以55 微米到 50 微米的间距完成,因此凸点密度高出约 16 倍。最常见和最高容量的用例是具有 TSMC CoWoS(基板上晶圆上芯片)的 Nvidia 数据中心 GPU。台积电将有源芯片封装在只有互连和微凸点的晶圆上。然后使用传统方法将这叠芯片封装到基板上。

其他示例基本上包括每个带有 HBM 的处理器。HBM 是作为一种阶梯函数增加内存带宽的方法而建立的,这种方法高于传统形式的 DRAM。它通过使用更宽的内存总线来实现这一点。这些宽总线会产生与 IO 计数相关的问题,但 HBM 是从头开始设计的,以便在同一包内共存。这颠覆了 IO 问题,同时也允许更紧密的集成。

2.5D 的更多示例包括基于Intel EMIB 的产品、Xilinx FPGA、AMD 最新的数据中心 GPU 和Amazon Graviton 3.

3D 封装将一个有源芯片封装在另一个有源芯片之上。这最初是由英特尔提供的55 微米间距的逻辑硅片,但批量用例将是 36 微米或更小。台积电和 AMD 将推出 17 微米间距的 3d堆叠 V-cache。该技术从凸块转移到硅通孔 (TSV),并且具有更大的扩展空间。

索尼制造的 CMOS 图像传感器等其他应用已经采用 6.3 微米间距。为了继续进行比较,36 微米间距的凸块密度高 31 倍,以17 微米间距实现的铜 TSV 的 IO 密度高 138 倍,索尼的 6.3 微米间距的CMOS 图像传感器的 IO 密度高 567 倍标准倒装芯片。

先进封装的出现,让业界看到了通过封装技术推动芯片高密度集成、性能提升、体积微型化和成本下降的巨大潜力。目前,人工智能(AI)、高性能计算、数据中心、自动驾驶汽车、5G都有先进封装的身影,应用领域逐渐扩大,各大厂商摩拳擦掌地为AI浪潮积极地做准备,一场先进封装技术竞赛已然拉开了帷幕。

下一篇:助焊剂残留物清洗

![[x]](/template/default/picture/closeimgfz1.svg)