因为专业

所以领先

将存储器叠层在逻辑器件上看似比较合理,这可以实现更大规模的小型化、性能和成本效益。然而,看似符合逻辑的想法却并非如此简单。因为逻辑处理器是逻辑加存储配置或叠层中价值较高的器件,逻辑器件制造商在将他们的逻辑器件与存储器件集成时遇到很大困难。他们预计购买晶圆形式的存储器,但这并不是他们自身的产品,因此他们对存储器件的测试良率、交互作用和质量非常关心。此外,存储器测试的专业性非常强,最好留给存储器制造商来完成,并可查看测试结果,以免遇到意想不到的复杂性和高成本。经过前期几次倒霉的尝试,大多数想将逻辑与存储器件集成在同一封装体内的逻辑器件制造商都在焦虑地寻找更好的方法。

PoP解决方案

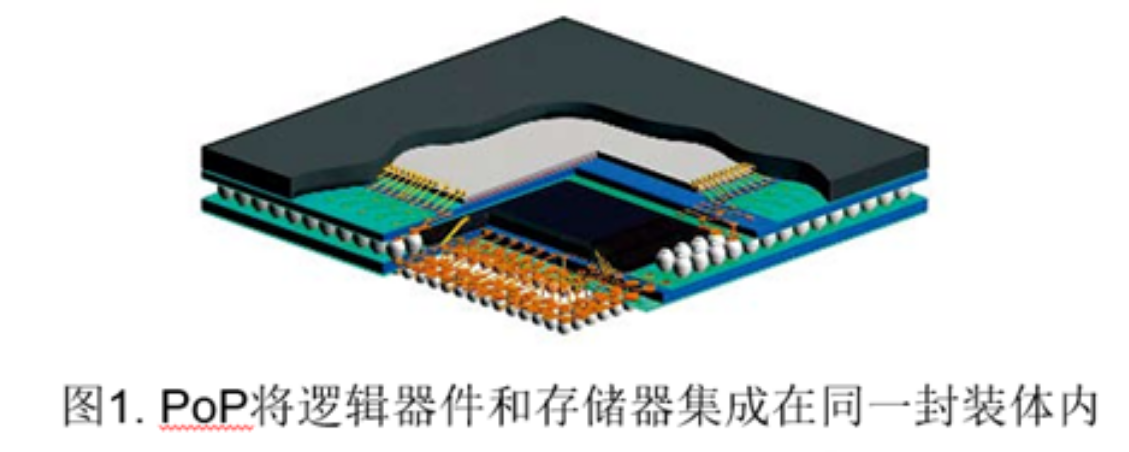

PoP被认为是更好的方案,可在同一封装体内集成逻辑和存储器件(图1)。PoP的底部可

容纳逻辑器件,这种封装的底面可以处理高引脚数,要求器件采用微小的焊球间距。PoP的顶部可容纳存储器件或器件叠层。由于存储器件一般要求引脚数较低,可以通过周边阵列来处理,即在两个封装体互连的封装边缘处。封装体的底部可以由逻辑器件制造商来制造和测试——每个都会影响他们核心的能力和技术。在一个封装内集成外来的芯片所造成的责任问题可以消除了,因为每个制造商只负责他们自己的封装。终端用户、手持设备制造商可以通过调配来获利,即传统的存储器供应商来供应顶部封装,逻辑器件供应商来提供底部封装。他们的配置也比较灵活,有多个存储器货源和封装类型,可以与多个处理器封装类型和供应商相匹配。

如果逻辑器件和存储器件都被集成到同一个叠层封装中,那么手机制造商则无需再列出特定的器件组合方案。通过JEDEC的电学(取决于内部存储器的配置)和机械标准,可以灵活地实现顶部存储器件封装与底部逻辑器件封装的组合。底部封装也遵守JEDEC的机械标准。这样的标准化允许制造商设计并生产能够彼此兼容的产品,这也是为什么PoP终于成熟,并且在过去几年内投放市场进行大量生产的一个基本原因。

今天,将PoP投入量产并不轻松,如同所有新型封装技术一样,还有很多障碍需要克服。为实现灵活的PoP结构,封装叠层需要在PCB上同时塑模并再回流。此前并不容易实现,需要手机制造商或者其电子制造服务提供商(基板组装)进行开发和优化。两个球栅阵列(BGA)封装不但可以在相互的顶部进行再回流,而且再回流两个非常薄的、相对大些、窄间距的BGA在某种程度上也是新的挑战。由于两种封装的间距都相对较窄(一般为0.65 mm的间距或者小于封装体到封装体之间的互连),再回流过程中每个封装体能够承受的翘曲量是非常有限的。以前,再回流过程中封装翘曲并不是影响表面贴装良率的主要考虑因素。

现在已经可以度量并控制封装翘曲。使问题进一步复杂的原因是该结构很难控制底部PoP的翘曲。底部PoP的外围缺乏模塑密封材料,可以互连到顶部封装(图2)。因此,外围由一个无支持的封装基板组成。为了降低整个叠层PoP的高度,基板又被尽可能地做薄。因为基板会由于再回流的温度而膨胀(所有PoP都在稍高的再回流温度下采用无铅焊球,而非共晶锡铅焊球),这样的配置会内在的导致翘曲。封装尺寸、器件尺寸、基板厚度和成分、模塑密封材料、裸片粘接厚度和材料全都在决定底部PoP翘曲中发挥重要作用。同样地,必须对它们进行优化才可能生产出满足表面组装良率要求的底部PoP。一般而言,如果PoP叠层无法再回流到PCB上,就无法选择重做,因此对于基板组装时初次通过的良率要求是非常高的。

控制顶部封装的翘曲也是一项挑战。顶部PoP内部可叠层2至5片裸片。这些器件的尺寸各式各样:一些器件尺寸相同或相近,需要在叠层裸片之间采用间隔夹层,这样才能使引线键合到基板上。虽然再回流时观察封装的顶部会发现一般底部PoP的外形有些凹陷,然而顶部PoP的外形也会凹陷或凸起。尽管顶部PoP将模塑密封材料扩展到封装边缘,通常产生的翘曲小于底部PoP,顶部PoP的翘曲必须经常容忍底部封装的翘曲或者保持绷紧状态以允许底部封装中更高的翘曲。封装材料和厚度的优化对于顶部PoP实现合格的表面组装良率是非常重要的。再回流过程中以顶部和底部封装为目标的翘曲最初大约80μm。然而,随着大量的调查,对于0.65 mm的封装到封装互连间距,一些顾客已经将翘曲目标降低到60μm。

PoP堆叠芯片清洗:PoP堆叠芯片/Sip系统级封装在mm级别间距进行焊接,助焊剂作用后留下的活性剂等吸湿性物质,较小的层间距如存有少量的吸湿性活性剂足以占据相对较大的芯片空间,影响芯片可靠性。要将有限的空间里将残留物带离清除,清洗剂需要具备较低的表面张力渗入层间芯片,达到将残留带离的目的。 研发的清洗剂具有卓越的渗入能力,以确保芯片间残留活性剂被彻底清除。

针对先进封装产品芯片焊后封装前,基板载板焊盘、电子制程精密焊后清洗的不同要求, 在水基清洗方面有比较丰富的经验,对于有着低表面张力、低离子残留、配合不同清洗工艺使用的情况,自主开发了较为完整的水基系列产品,精细化对应涵盖从半导体封装到PCBA组件终端,包括有水基清洗剂和半水基清洗剂,碱性水基清洗剂和中性水基清洗剂等。具体表现在,在同等的清洗力的情况下, 的兼容性较佳,兼容的材料更为广泛;在同等的兼容性下, 的清洗剂清洗的锡膏种类更多(测试过的锡膏品种有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;测试过的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,离子残留低、干净度更好。

想了解更多关于先进封装产品芯片清洗的内容,请访问我们的“先进封装产品芯片清洗”产品与应用!

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)