Chiplets如此重要的确切原因分析及Chiplets封装清洗

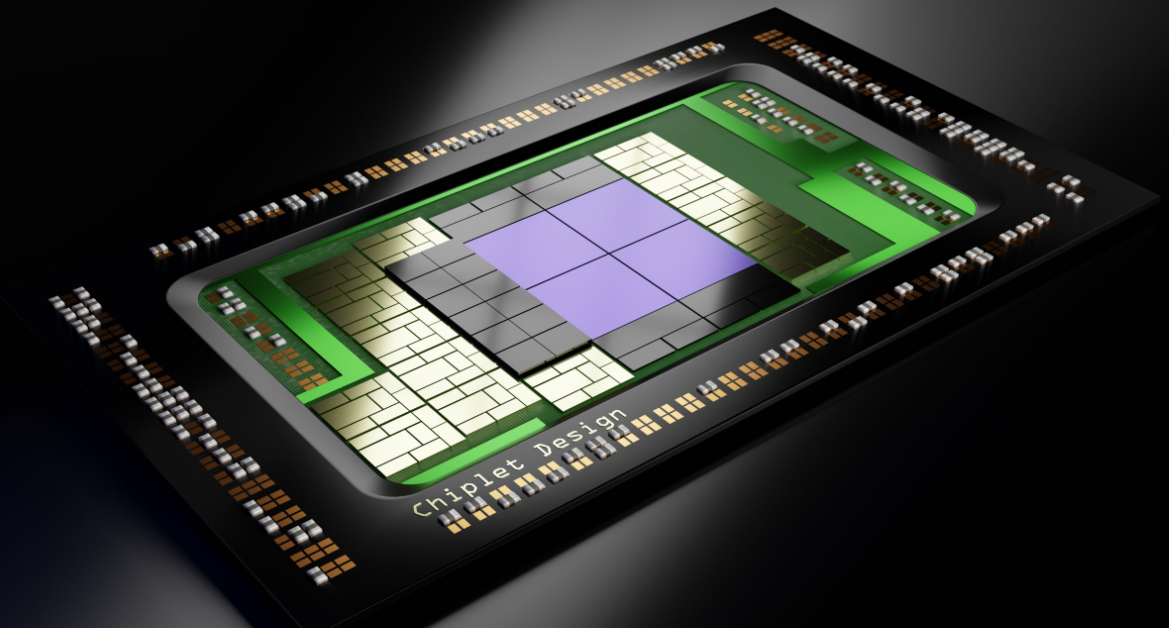

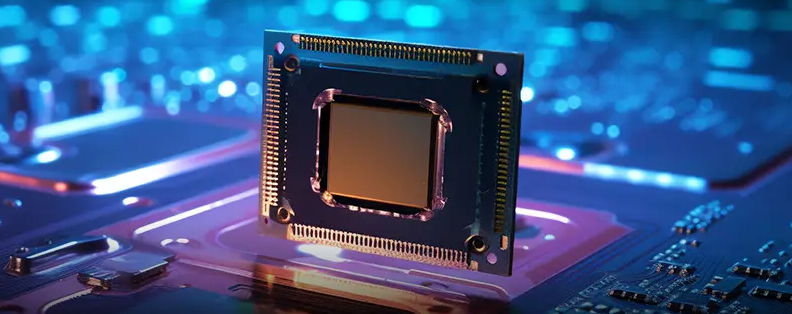

Chiplets是分隔式的处理器。不是将每个部分合并到一个芯片中(被称为单片机的方法),而是将特定的部分作为独立的芯片来制造。然后,这些独立的芯片通过一个复杂的连接系统被安装在一起,成为一个单一的封装。这种安排使能够让使用最新的制造方法的部件尺寸缩小,提高了工艺的效率,使其能够装入更多的部件。芯片中不能明显缩小或不需要缩小的部分可以用更旧的、更经济的方法生产。虽然制造这种处理器的过程很复杂,但总体成本通常较低。此外,它为处理器公司提供了一个更易于管理的途径来扩大其产品范围。为了充分理解为什么处理器制造商转向芯片,我们必须首先深入了解这些设备是如何制造的。CPU和GPU开始时是由超纯硅制成的大圆盘,通常直径略小于12英寸(300毫米),厚度为0.04英寸(1毫米)。这块硅片经历了一系列复杂的步骤,形成了不同材料的多层--绝缘体、电介质和金属。这些层的图案是通过一种叫做光刻的工艺创建的,在这种工艺中,紫外线通过放大的图案(掩膜)照射,随后通过透镜缩小到所需的尺寸。该图案以设定的间隔在晶圆表面重复出现,每一个都将最终成为一个处理器。由于芯片是长方形的,而晶圆是圆形的,图案必须与圆盘的周边重叠。这些重叠的部分最终会被丢弃,因为它们是无功能的。一旦完成,将使用应用于每个芯片的探针对晶圆进行测试。电检结果告知工程师关于处理器的质量与一长串标准的关系。这个初始阶段被称为芯片分选,有助于确定处理器的 "等级"。例如,如果该芯片打算成为一个CPU,那么每个部分都应该正确运作,在特定的电压下在设定的时钟速度范围内运行。然后根据这些测试结果对每个晶圆部分进行分类。完成后,晶圆被切割成单独的碎片,或称 "模具",可供使用。然后,这些模具被安装在一个基板上,类似于一个专门的主板。处理器经过进一步的包装(例如,用散热器),然后就可以进行销售了。整个过程可能需要数周的制造时间,台积电和三星等公司对每个晶圆收取高额费用,根据所使用的工艺节点,费用在3000至20000美元之间。"工艺节点 "(Process node)是用来描述整个制造系统的术语。历史上,它们是以晶体管的栅极长度命名的。然而,随着制造技术的改进,允许越来越小的组件,命名不再遵循芯片的物理方面,现在它只是一个营销工具。然而,每一个新的工艺节点都会带来比前者更多的好处。它的生产成本可能更低,在相同的时钟速度下消耗更少的功率(或者相反),或者具有更高的密度。后者衡量的是在一个给定的芯片区域内可以容纳多少元件。在下图中,你可以看到这些年来GPU(你在PC中发现的最大和最复杂的芯片)的发展情况。

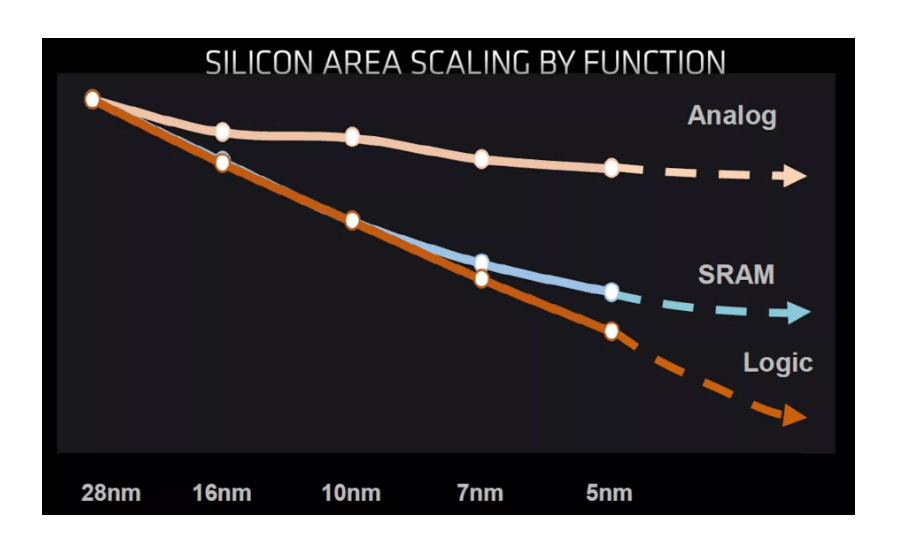

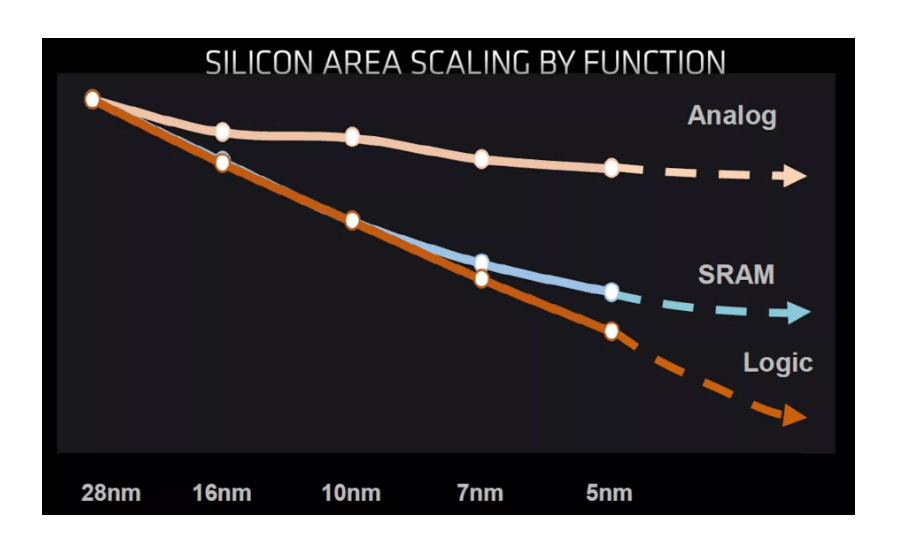

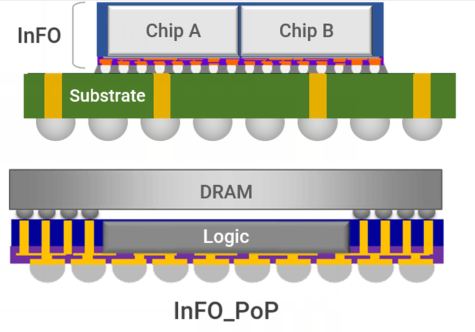

工艺节点的改进为工程师提供了提高其产品能力和性能的手段,而不必使用大而昂贵的芯片。然而,上图只说明了部分情况,因为不是处理器的每个方面都能从这些进步中受益。芯片内的电路可以被分配到以下几大类中的一类:(1)逻辑,处理数据、数学和决策;(2)存储器,通常是SRAM,用于存储逻辑的数据;(3)模拟 ,管理芯片和其他设备之间信号的电路。当逻辑电路随着工艺节点技术的每一次重大进步而继续缩小时,模拟电路几乎没有变化,SRAM也开始达到极限。

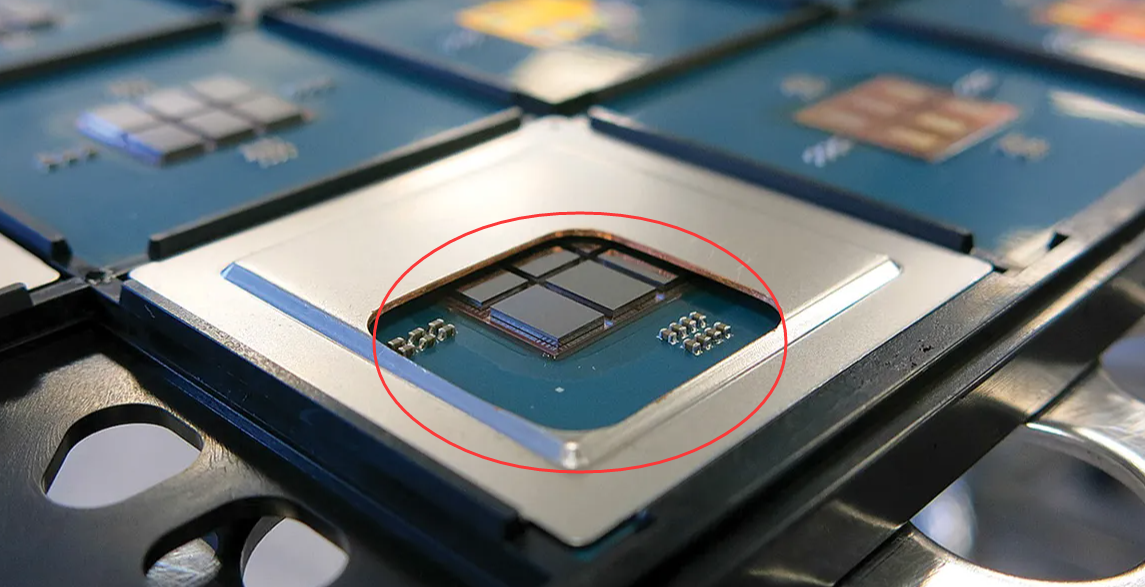

虽然逻辑仍然构成了芯片的最大部分,但今天的CPU和GPU中的SRAM数量在近年来有了显著增长。例如,AMD在其Radeon VII显卡中使用的Vega 20芯片的L1和L2缓存合计为5MB。仅仅两代GPU之后,Navi 21就有超过130MB的各种缓存--比Vega 20多了25倍,令人瞩目。可以预期,随着新一代处理器的开发,这些水平将继续提高,但由于存储器的规模没有像逻辑那样缩小,在同一工艺节点上制造所有电路的成本效益将越来越低。在一个理想的世界里,人们在设计芯片时,模拟部分在最大和最便宜的节点上制造,SRAM部分在更小的节点上制造,而逻辑部分则保留给绝对尖端的技术。不幸的是,这在实践中是无法实现的。然而,存在一种替代方法。尽管在半导体制造方面取得了巨大的技术进步,但每个部件可以缩小的程度是有明确限制的。为了继续提高芯片的性能,工程师们基本上有两个途径:增加更多的逻辑,用必要的内存来支持它,以及提高内部时钟速度。关于后者,一般的CPU在这方面已经多年没有明显的变化了。AMD的FX-9590处理器,从2013年开始,在某些工作负载中可以达到5GHz,而其当前型号的最高时钟速度是5.7GHz(Ryzen 9 7950X)。英特尔最近推出了酷睿i9-13900KS,在合适的条件下能够达到6GHz,但其大多数型号的时钟速度与AMD的相近。然而,改变的是电路和SRAM的数量。前面提到的FX-9590有8个核心(和8个线程)和8MB的L3缓存,而7950X3D拥有16个核心、32个线程和128MB的L3缓存。英特尔的CPU在核心和SRAM方面也有类似的扩展。Nvidia的第一个统一着色器GPU,即2006年的G80,由6.81亿个晶体管、128个内核和96 kB的二级缓存组成,其芯片面积为484 mm2。快进到2022年,当AD102推出时,它现在由763亿个晶体管、18432个内核和98304 kB的二级缓存组成,芯片面积为608 mm2。1965年,飞兆半导体公司的联合创始人戈登·摩尔(Gordon Moore)观察到,在芯片制造的早期,在固定的最低生产成本下,芯片内的元件密度每年都在翻番。这一观察被称为摩尔定律,后来根据制造趋势,被解释为 "芯片中的晶体管数量每两年翻一番"。近六十年来,摩尔定律一直是对半导体行业发展进程的合理准确描述。CPU和GPU在逻辑和内存方面的巨大进步是通过工艺节点的不断改进实现的,这些年来,组件变得越来越小。然而,这种趋势不可能永远持续下去,无论出现什么新技术。像AMD和英特尔这样的公司并没有等待这个极限的到来,而是转向了Chiplets,探索它们的各种组合方式,以继续在创造更强大的处理器方面取得进展。几十年后的今天,普通的个人电脑可能是由手掌大小的CPU和GPU组成的,但是剥开散热片,你会发现有许多微小的芯片--不是三四个,而是几十个,都巧妙地拼接和堆叠在一起。芯粒-先进芯片封装清洗:

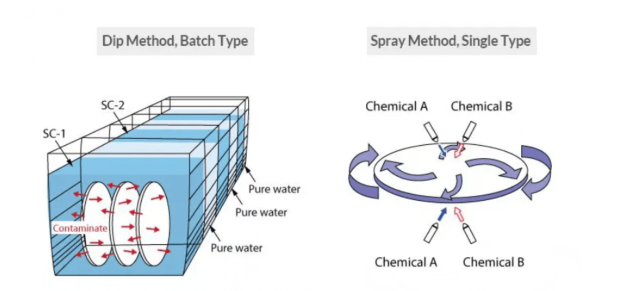

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用

水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)