因为专业

所以领先

首先,我们先要了解一下,什么是芯片的“封装”。芯片从设计到生产再到消费者手中是个极其复杂的过程,设计公司做完逻辑和物理设计,将最终设计结果交给芯片代工厂。代工厂经过无数复杂的流程,最终会在一块大的晶圆上做出许许多多的小芯片。而这一个个的小芯片,则被称为“die”。为什么要叫这么一个不吉利的名字?有一种说法是说,早期芯片生产工艺水平不足,切割出的芯片良品率很低,经常就“die”了,因此,工程师们才给它取了这么一个自嘲的名字。而从这个“小道消息”中,各位读者应该能意识到,die非常非常脆弱,因此不能直接使用,需要再给它加上一层保护壳,而这个过程,就叫做“封装”。简单点说,封装技术需要将die固定在基板(substrate)上,然后将die上的引脚连接到芯片外壳的引脚上。

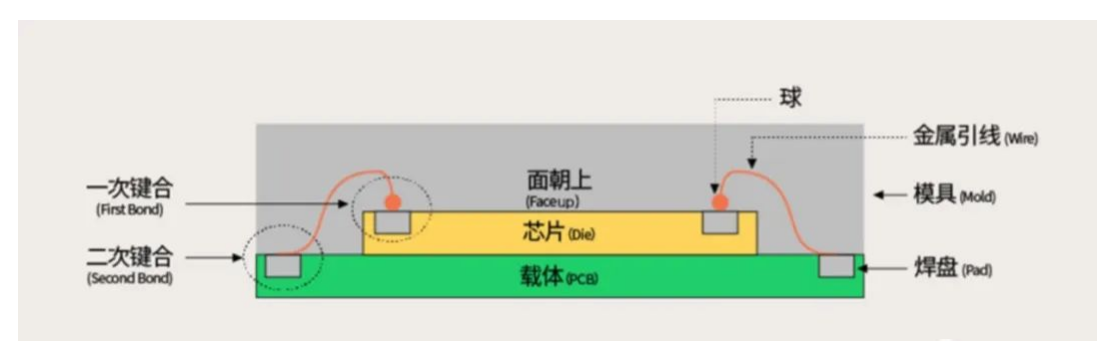

最基础的封装工艺即为:引线键合(wire-bonding)封装,其整体上十分简单,就是把die正面朝上固定到基板之上,再用导线,将die的引脚和基板连接(称之为‘键合’),最后把整个芯片封装起来,密封用的材料有塑料,陶瓷等。这种封装技术的优点是生产工艺相对简单,成本较低;缺点是封装完的芯片尺寸比die的尺寸大许多,且芯片管脚数受限。

引线键合(wire-bonding)封装

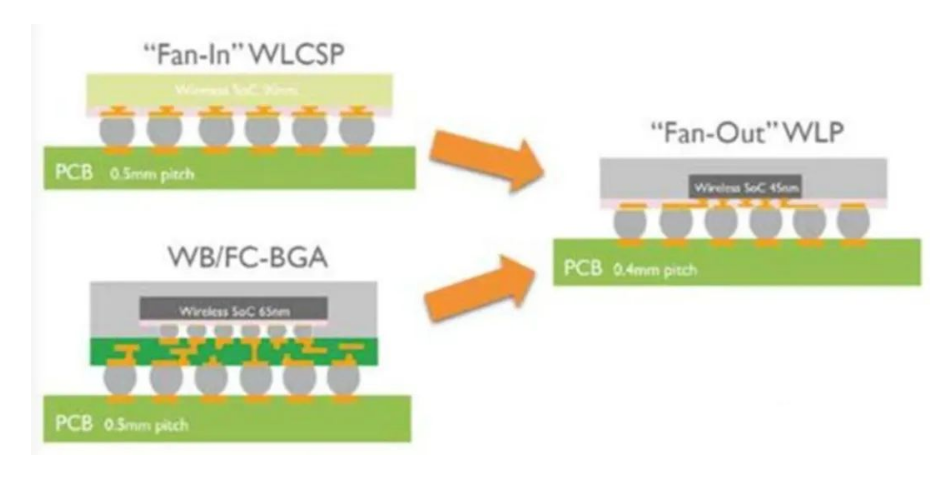

之后,随着技术的进步,又出现了“倒装”,即将die的正面朝下,提前做好焊点的技术,倒装的应用使得封装尺寸和芯片接近,并且有更多的引脚,但是随着芯片功能越来越多,I/O数量急剧增加,传统的封装已经难以满足要求。后来据此还衍生出了Fan-Out WLP(Wafer Level Packages),也叫FOWLP技术,但是文章篇幅有限,有兴趣的读者可以自行了解。

上文中所言都是单独die的封装,一颗完整的现代芯片,单个die是远远不够的,需要将多个die封装在一起,而这之中的封装方式便是2D,2.5D,3D封装。

2D封装技术

最简单的办法,便是最简单的“2D封装”,即:将多颗die正面朝下,焊接到基板上,die与die之间的互连就靠基板上的走线。这种办法的缺点是基板上的布线密度低,因此die与die之间的互连受限。而为了解决布线密度的问题,芯片封装来到了2.5D阶段。

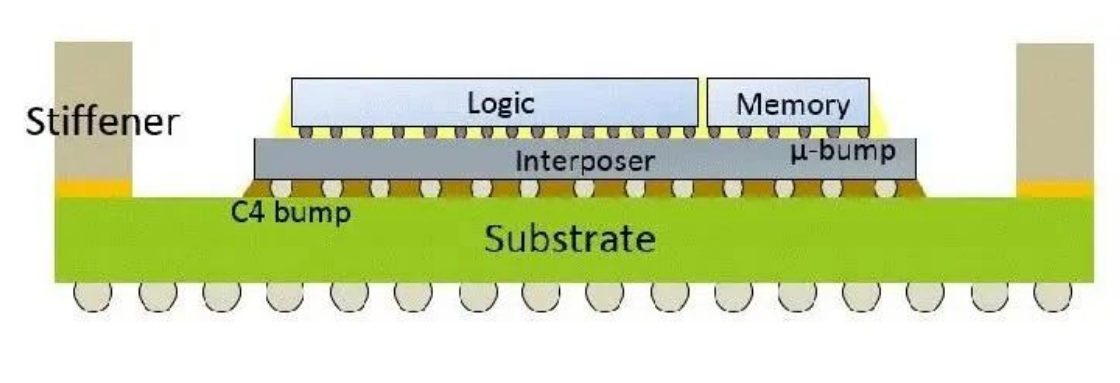

2.5D封装技术

2.5D封装之中的代表就是台积电推出的CoWoS技术。台积电为了解决die和die之间的布线密度问题,在die和基板之间加入了一层“硅中介层”。Die和die之间并不直接连接,而是与中介层连接,也就是说硅中介层充当了die-die互连和die-substrate互连角色。由于中介层的布线可以直接使用半导体工艺制造,因此其布线密度得以大幅提升。这种技术的缺点也是十分明显,由于中介层也是使用半导体工艺制造,其成本很难下降,其面积也严重受到半导体工艺的限制,很难做大。

2.5D封装

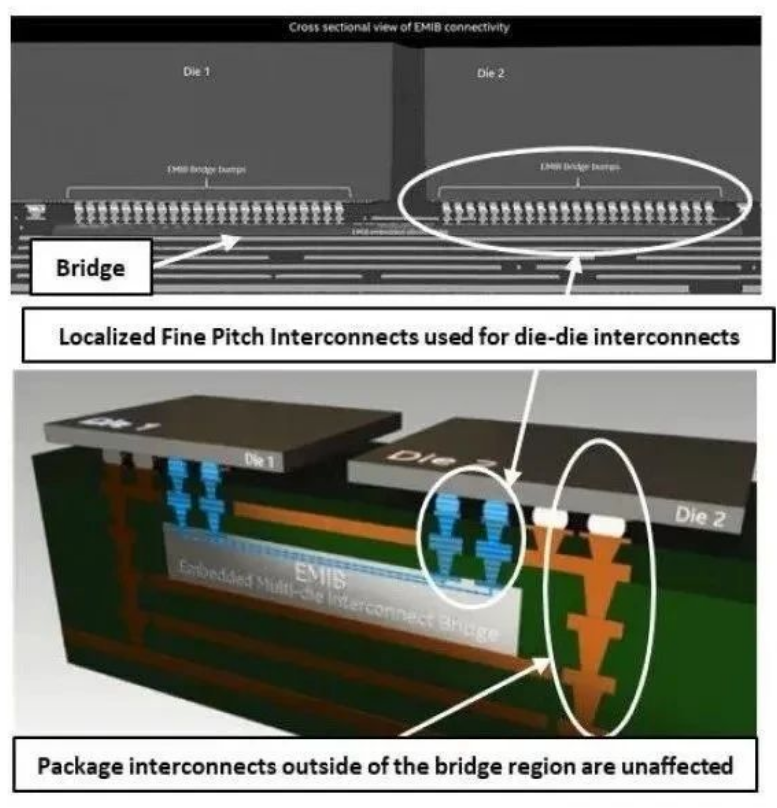

随后,为了降低这成本不低的中介层面积,英特尔发明了EMIB,将die-die的互连用“硅桥(Si Bridge)”实现,且硅桥嵌入在基板内部,die-substarte的连接通过传统方法实现。这种做法可以大大降低硅中介层的面积,减少成本,减轻多die封装的限制。

英特尔EMIB封装

从上文中的描述中各位读者也许可以发现,无论是2D封装还是2.5D封装,所有的die都是在同一平面之内,所以,这也就注定了要想用更多的die,就要更大的封装面积,这对于需要小型化的芯片来说无疑是背道而驰,注定了一颗芯片中不能有太多die。那怎么办呢?工程师们给出了他们的解决方案:把die像大楼一样,垒起来!

从2D到3D,这就是一个很大的进步。2D到3D,包含晶体管的架构,从原来平坦式的晶体管,现已变成立体式晶体管。除了在芯片上的晶体管开始变成3D之外,封装部分也把它变成了3D。

3D封装技术

在3D封装中,工程师们通过垂直堆叠芯片,用更短的互连和高带宽连接起来,进一步弥补了二维封装设计中的缺陷。在传统的2D封装中,往往需要大量远距离连线,电路中控制电容、电阻的充放电造成的信号延迟,即RC延时难以控制。为了提高信号传输速度,必须降低RC延迟,那么用3D封装的短程垂直互连来替代2D封装的长程互连是封装工艺技术向更高阶发展的必然趋势。

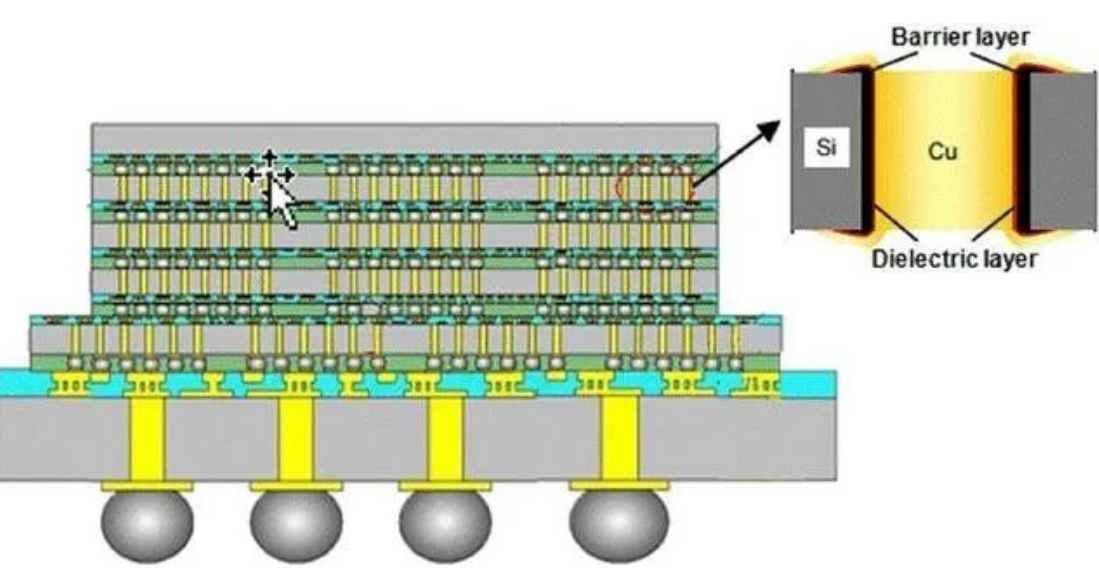

而实现在3D封装的关键技术就是TSV硅通孔技术。简单来讲,TSV技术通过在芯片与芯片之间、晶圆和晶圆之间制作垂直导通,通过导电物质的填充实现硅通孔的垂直电气互联,它是目前唯一能实现垂直电互联的技术。这种技术看上去十分完美,但是难度太高,成本太大。试想一下,在又薄又脆弱的玻璃片上打很多通孔,再把这些经过处理之后更加脆弱的芯片垒成“摩天大楼”,听着就十分困难。因此,TSV技术在1958年被威廉·肖特基(William Shockley)第一次申请专利之后,直到40多年后的21世纪才逐渐走向商用,2000 年,日本分别率先研发出第一款三层堆叠的图像传感器和三层堆叠的存储器件。2005 年,10 层堆叠的存储芯片被研制出来。2007 年集成 TSV 的 CIS 芯片由 Toshiba 公司量产商用,同年 ST Microelectronics 和 Toshiba 一起推出 8 层堆叠的 NAND 闪存芯片。2013 年第一款 HBM 存储芯片由韩国 Hynix 推出。2015 年,第一款集成 HBM 的 GPU 由 AMD 推出。

目前,所有的3D封装技术都是基于TSV技术之上,随着市场对于芯片算力要求的不断提高,和摩尔定律逐渐难以“遵守”的压力,各大厂商纷纷推出自己的技术,比较有代表性的是台积电的SoIC技术和英特尔的Foveros技术。

芯片封装清洗:

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

上一篇:三防漆清洗剂之三防漆的作用

![[x]](/template/default/picture/closeimgfz1.svg)