因为专业

所以领先

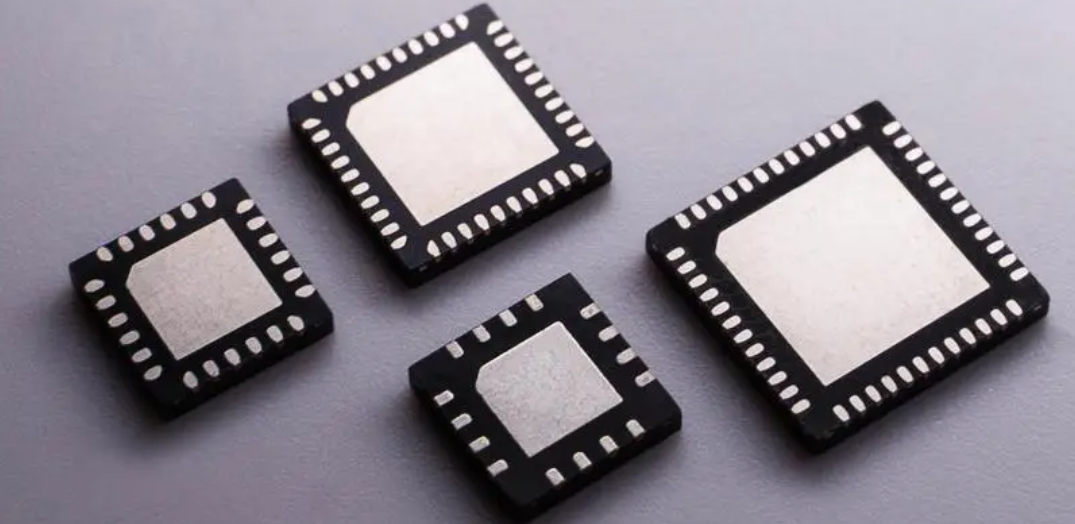

三维(3D)封装

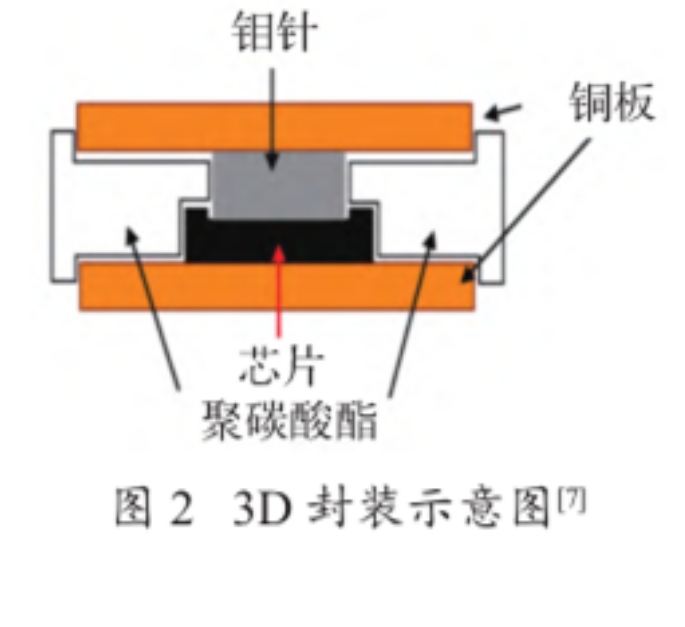

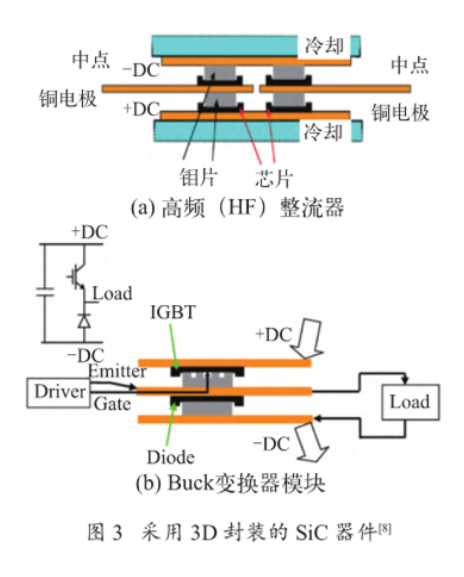

3D 封装(示意见图 2)技术将 SiC 模块的上桥臂直接叠加在下桥臂,上下叠加后可以减小桥臂中点的连接线(见图 3),该封装技术可将模块寄生电感降至1 nH 以。

2010 年格勒诺布尔电气工程实验室 VAGNON [9]利用 3D 封装技术搭建了单相 400 V/40 A 高频(HF)整流器及 Buck 变换器模块。实验结果表明采用 3D 封装技术后 IGBT 在关断时仅有 10%的电压过冲,且在导通时几乎没有欠压。因此 3D 封装技术可以基本消除共源极电感,同时共模电流也得到了很好的抑制。

2015 年,欧洲研发中心的 REGNAT [10] 提出了一种基于印刷电路板(PCB)嵌入式芯片技术的新型 3D 封装。利用 PCOC(片上电源)技术将 SiC MOSFET 芯片嵌入 PCB 内部实现较低的电感路径和共模电容。

文献搭建了如图 4 所示的模块,该模块具有30 mm×30 mm×2 mm 厚的 PCB,上下表面为 105 μm铜平面,模块边缘有 16 个去耦电容。为了在阻抗测量期间对开关状态下的换向单元进行建模,在前环和后环中未填充的芯片位置通孔的加和减端之间实现了短路。测量连接器位于两个自由边上,因此只需反转模块即可测量前换向环路和后换向洛普阻抗。测量结果为前环的功率环路电感为 0.23 nH,后环的电感为0.21 nH,因此采用嵌入式芯片技术的 PCOC 模块可实现紧凑、高密度的功率模块,同时可大幅降低回路的寄生电感,使其适用于具有快速导通和关断时间的宽禁带半导体器件(如 SiC 等)。

3D 封装技术消除了模块中的键合线,可以有效提高器件的功率密度,充分发挥 SiC 器件的高频优势。同时采用 3D 封装技术可以降低回路的寄生电感值,减小模块体积,从而推进电力电子器件走向高频、高效、高功率密度。

三维(3D)封装先进芯片封装清洗:

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)