因为专业

所以领先

SiP涉及到许多互连情况,例如芯片与芯片、芯片与基板以及基板和PCB之间,互连保证了电信号的传递,事关信号传输以及封装整体的稳定性,传统的封装互连方法主要是引线键合以及微焊点连接随着对封装集成度要求的增加,逐渐出现了倒装、晶圆级封装、硅通孔等一系列先进封装互连技术.本节主要介绍2.5D/3DSiP所需的互连技术.

倒装连接基于封装密度的提高以及信号传输路径的考量,倒装芯片技术在电子封装中得到了各种应用.与传统的引线键合相反,在倒装芯片封装中,硅芯片的有源侧面朝下,并通过焊点或凸块连接到基板,如此以来减小了单个芯片的占地尺寸,并且大大缩短了信号传输路径与引线键合相比,倒装芯片在输入/输出密度、电气性能、尺寸、生产成本和热性能方面无疑更具优势.

在技术要求上面,倒装芯片封装带来的主要挑战是由于焊料凸块、硅芯片和有机衬底之间的CTE不匹配而导致的热机械应力积聚,随着电子设备的持续使用,芯片封装的互连焊点会经历热循环,最终会导致疲劳或电气故障.这种CTE失配问题有两种解决思路:焊料成分人手和通过底部填充(Underfill)工艺解决.锡铅焊料是电子封装中常用的焊点材料尽管Pb和富含Pb的金具有凸块焊料最理想的特性之一,但是鉴于环境保护问题,含铅焊料逐渐被摈弃.目前对于无铅钎料的研究大多集中于寻找共晶锡铅合金的替代材料上.目前常用的无铅焊料为富Sn合金焊料,比较受青睐的有Sn-Ag和Sn-Ag-Cu 系合金.通常,为了改善焊点机械性能和稳定性,心片和基底之间的狭窄间隙填充有UUnderfill流体,Underfill一般是环氧树脂与熔融二氧化硅填料的均匀混合物,它将重新分配热机械应力,使其远离互连,在固化后,填充凸块阵列间隙的Underfill将化学硬化以形成封装凸块的保护层.

2.晶圆级封装

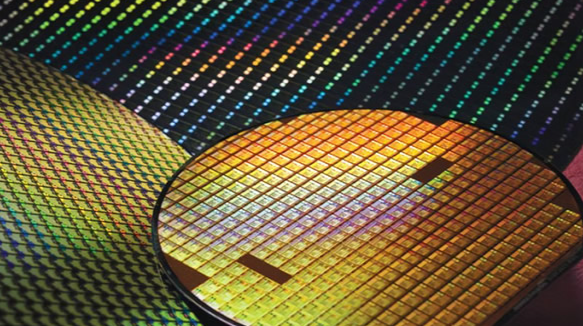

传统的封装发生在晶圆被切片之后,而晶圆级封装是对晶圆先封装后切片.晶圆级封装的优势是大大减小了封装的尺寸,使其能够与裸片尺寸一致,从而达成芯片封装小型化、轻量化的目标.此外,晶圆级封装通过重布线层(RDL)将裸片上的接口引出,因此,相较于普通封装工艺,晶圆级封装减少了一层基板的使用.晶圆级封装又可分为扇入型晶圆封装(Fan-in WLP)和扇出型晶圆封装(Fan-out WLP)两种,如图7所示,二者的区别在于RDL上的I/O数量是否超出裸片面积范围.对扇人型晶圆级封装来说,I/O 分布不超过芯片的覆盖面积,因此,裸片面积占据了封装面积的 100%.随着需求的增加,芯片所需的I/O 接口数量增多,扇人型品圆级封装所能支持的I/O 接口有限,因此,需要 RDL将 I/O扩展到裸片面积以外,这就是扇出型晶圆封装.

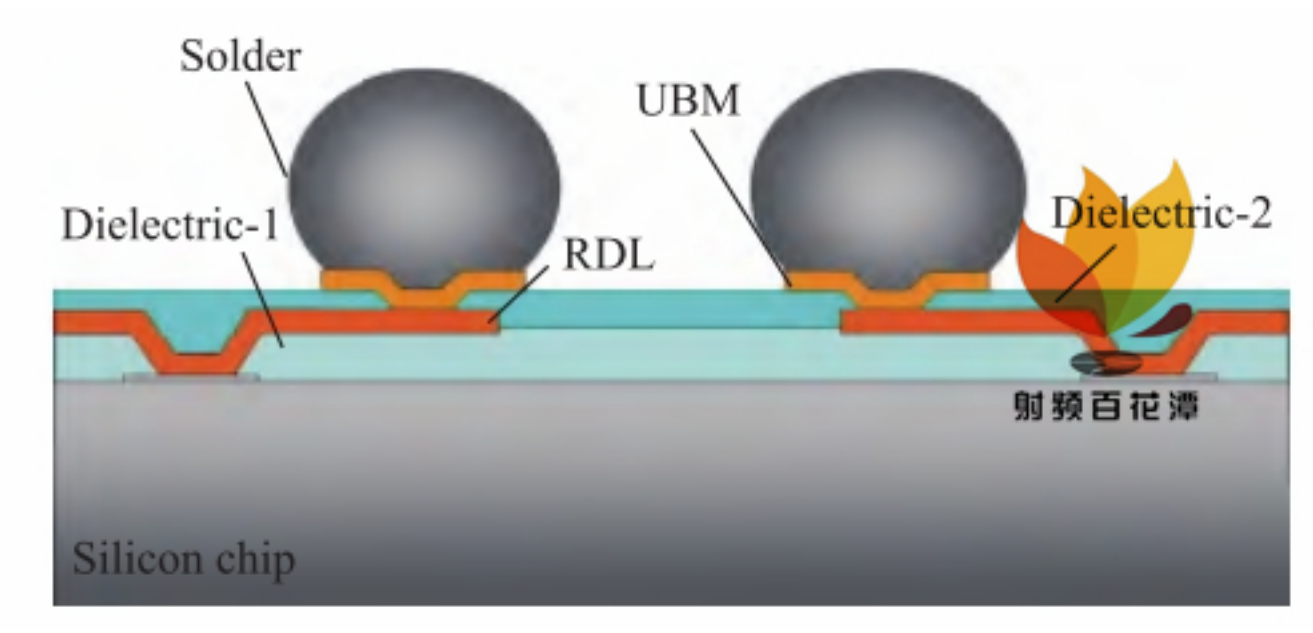

无论是扇人型还是扇出型晶圆级封装,RDL技术在其中都是不可或缺的,RDL将IO接口重新排布,并将信号传递至焊点(Solder).RDL是在晶圆表面沉积金属层和绝缘层形成相应的金属布线图案,采用高分子薄膜材料和ACu金属化布线对芯片的I/O焊盘重新布局成面阵分布形式,将其延伸到更为宽松的区域来植锡球.在2.5D封装的Interposer中RDL也发挥着作用.可以说,在先进封装中,RDL发挥着很重要的作用。

为了提高焊点的可靠性,对 RDL进行精心的设计是必要的.RDL改进的思路之一是在焊料和硅芯片之间添加一个缓冲层,例如有研究者设计了一种聚合物上焊点结构,如图8所示.可以看到,RDL上方和下方都有两个介电层,这将提高互连强度,因为聚合物介电层可以使芯片和PCB之间的应力得到缓冲.此外,RDL提升的另一个思路是RDL与焊点材料配合,共同来提高互连的可靠性

2.2扇出型晶圆级封装

扇出型晶圆封装可以调整RDL来适应大数量接口的需求,并且其封装尺寸也更小,这些特征有助于封装结构的热性能和电性能.扇出型晶圆级封装的这种特点使其在5G毫米波器件的封装中广受关注.

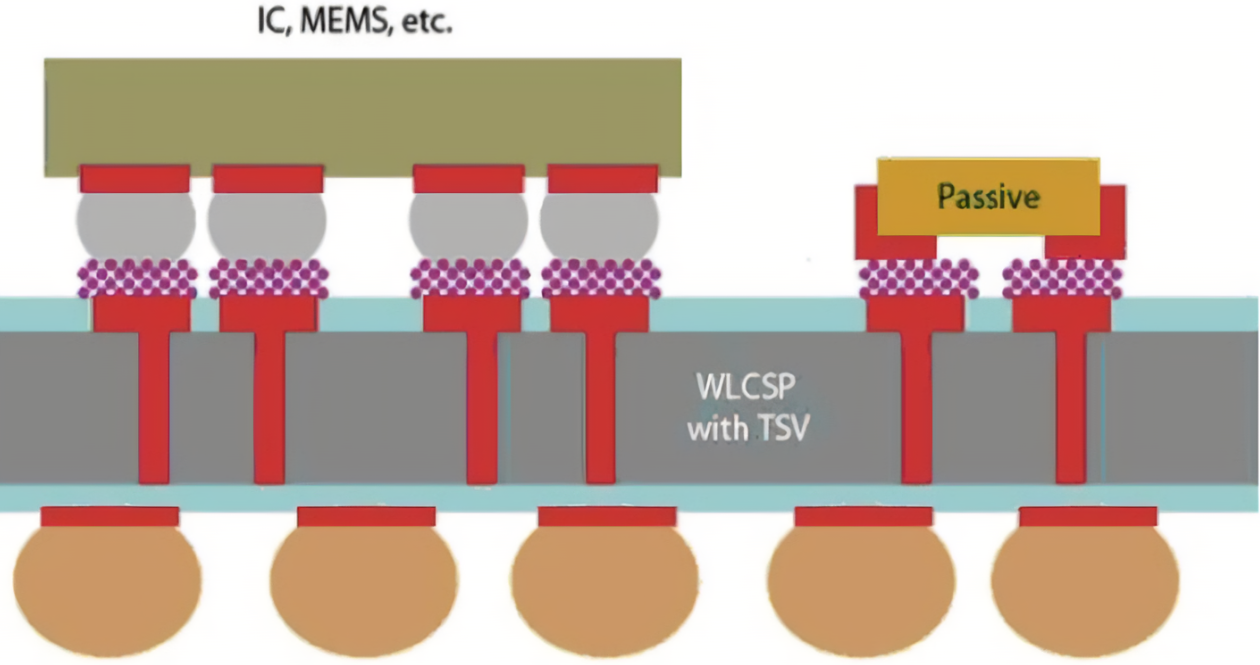

3.硅通孔(TSV)技术

5.封装天线(AiP)

AiP技术是将一元或多元天线集成到封装内部天线技术,其典型方案是采用集成电路封装工艺AiP 依靠 3D 封装技术,大大缩短了馈线长度,从而降低了互连损耗,提高了系统电源效率.AiP的优点在于它在单独的基板上实现,独立于RF芯片,且该基板可以专门用于辐射元件及其馈线,也可以充当收发器组件和异构集成的封装.

总的来看,AiP有两种结构:一种是倒装芯片结构,一种是嵌入式芯片结构.倒装芯片结构中,芯片采用倒装技术被与基板一侧连接,而天线阵列被布置在基板的另一侧.嵌入式芯片结构中,芯片嵌入基板内部,而天线阵列被布置在基板一层.由此可见,AiP 技术的关键在于先进封装互连技术与基板材料的选择这两方面内容已在上文中阐述,在此不再赘述.

目前,AiP正被广泛应用于毫米波器件,被认为是未来毫米波天线封装的最佳解决方案.Gu等人在基站用有机层压基板的AiP方面取得了开创性进展他们设计了一个包括64个阵列嵌入式天线的芯片AiP.天线阵列在Tx模式和±40°扫描范围下,等效全向辐射功率(EIRP)超过50dBm.在产业化应用方面目前一些企业,包括IBM、Intel、Samsung等均已开始将 AiP 作为其产品的天线封装方案.

片上天线是采用片上金属化连线工艺集成制作的天线.AoC 技术与 AiP技术最根本的区别在于,芯片上天线没有与射频电路(RF)封装在一起,所以射频电路不存在任何形式的互联,天线自己的功能结构基于单个模块上.其次,与 AiP相比,AoC 更小,只有几平方毫米.然而,AoC的缺陷在于,对于硅基AoC 而言,衬底的高介电常数和低电阻率严重降低了匹配带宽和辐射效率.

7.SiP芯片封装清洗:

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

上一篇:PCBA电路板上的残留物分析方法

![[x]](/template/default/picture/closeimgfz1.svg)