因为专业

所以领先

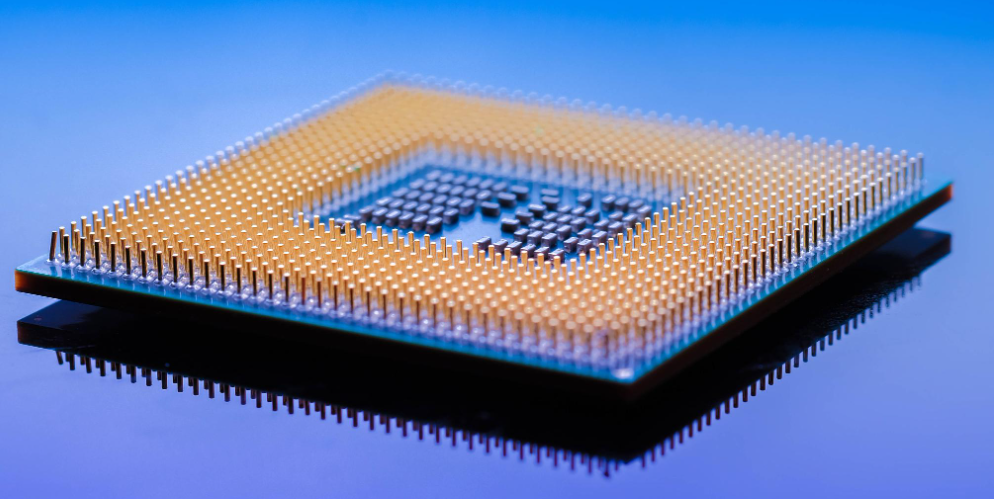

集成电路金属互连工艺是通过光刻将淀积的金属薄膜形成布线,将内部相互隔离的器件按照一定要求连接成电路,确保芯片电信号传输。

根据最小的金属线节距, 集成电路金属互连可以分为局部互连、 中间互连和全局互连。局部互连是指在器件层进行的互连,包括栅极多晶硅和底层金属互连,通常采用最小的金属线节距以减小线条的尺寸效应;中间互连金属层的拥挤程度相对较低, 因此允许放宽金属线节距并增加金属层厚度;全局互连是集成电路芯片的顶部布线层, 主要用于电源接入和信号输入/ 输出, 通常具有较大的金属膜厚和线节距, 但需要满足与芯片外部 (即封装) 连接有关的额外要求。

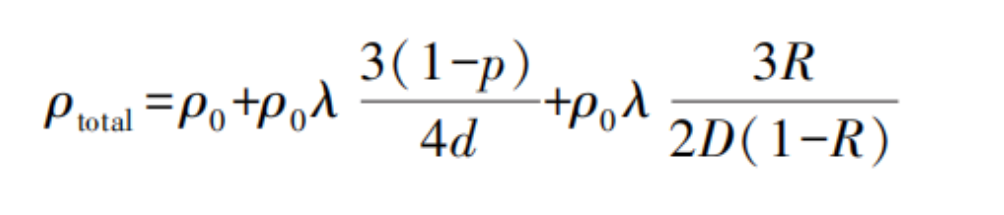

1997年,IBM实现了Cu大马士革工艺,由于铜具有更好的导电性和抗电迁移特性,制作金属互连的主要材料由早期的铝换成了铜。因此,目前铜互连成为芯片互连的主流工艺。与铝互连相比,铜互连具有更好的电阻性和可靠性。然而,随着技术节点的进一步发展,电阻的尺寸效应越发明显。根据Matthiessen定律,线路电阻率由体电阻率、 表面散射和晶界散射等因素决定, 其简化的表达式为:

式中:ρtotal是总电阻率;ρ0是体电阻率;λ 是电子平均自由程;d是薄膜平均厚度;p 是表面散射因子;D 是平均晶粒尺寸;R 是晶界散射因子。在7nm节点之前,互连导体的体电阻率通常是确定线路电阻的主要因素。然而, 从7nm技术开始,表面散射和晶界散射变得更加重要。随着互连线宽度的减小, 铜电阻的尺寸效应导致线电阻急剧增加, 严重影响了芯片的互连性能。

典型的Cu线结构

为了增加Cu的体积分数, 大量的研究致力于减小TaN阻挡层的厚度。随着晶体管尺寸的减小, 由于PVD 存在台阶覆盖率较低和顶部悬突的问题, 原子层沉积 (ALD)/CVD开始被引入, 以提高填孔性能和减小阻挡层厚度。经过研究发现,因此,将热ALD和PVD 相结合成为保持阻挡性并减小TaN 厚度的有效方法。

对于衬垫层的尺寸微缩, 人们也进行了广泛研究。尽管ALD/CVD方法可以解决台阶覆盖率和顶部悬突问题, 但用于生长Ta薄膜的反应源十分有限。因此, 人们开始考虑其他替代材料。其中,Ru因与ALD/CVD工艺的适用性及可以在没有PVD Cu籽晶层的情况下直接镀Cu,得到了广泛关注。此外,Co也被认为可以替代Ta作为衬垫层。虽然Ru衬垫层比Co衬垫层更适合于Cu电镀填充, 但由于表面和晶界散射的原因,Ru的电阻比Co的高约10%。此外,在抗电迁移方面,也已证明Co衬垫层优于Ru衬垫层。

为了充分发挥Ru衬垫层的优势,人们开始尝试改善其抗电迁移性能。从14nm技术代开始,Co顶覆盖层已成为一种标准工艺。通过增加Co顶覆盖层的厚度, 可以明显提高Ru 衬垫层的抗电迁移性能力。但当金属的半节距减小到10nm 以下, 阻挡层/ 衬垫层的最小厚度也将达到极限。

(3)自形成阻挡层

自形成Co基阻挡层(tCoSFB)工艺是一种具有应用潜力的Cu互连拓展技术。该工艺利用掺杂在Cu籽晶层中的Mn扩散至沟槽和电介质层的界面形成阻挡层。

tCoSFB的结构和工艺流程

tCoSFB工艺的优势为:由于Co衬垫层和Ta阻挡层的厚度共1nm,可以最大限度地提高布线中Cu的横截面积, 从而获得较低的线电阻。

(4)混合金属互连工艺

通孔对于片上系统的信号传输至关重要。当通孔的底部接触面积变小时,通孔电阻会显著增加。在通孔中引入无阻挡层金属尤为重要, 可显著降低通孔电阻。混合金属互连工艺是一种先使用无阻挡层金属Ru预填充通孔, 再用Cu填充剩余面积的方法。

双金属系统中的Cu混合金属互连工艺示意图

无阻挡层金属预填充有许多优势。预填充金属将Cu大马士革阻挡层的位置从孔的底部移到顶部,减小了高深宽比(AR)通孔的填孔难度,提高了台阶覆盖率,因此可以实现更薄的阻挡层。此外, 无阻挡层金属预填充工艺可以降低通孔的电阻, 减小RC延时, 从而显著提高电路的性能。最初, 通孔预填充工艺使用Co。然而,由于Co的电迁移问题, 需要使用TiN作为阻挡层, 而Ru无需阻挡层, 通过Ru预填充, 可使通孔电阻减小40%,同时实现与现有工艺方案相匹配的抗电迁移性能。

由TCR 实验得到的Ru、Co和Cu大马士革互连线电阻与横截面积的关系

通过DME制备的Ru和空气隙半大马士革结构

近年来, 由于Cu大马士革结构的诸多限制,Ru的半大马士革工艺因其与空气隙制备良好的工艺兼容性,被作为一种工艺选择得到广泛关注。然而,并不存在一种金属互连工艺能够同时满足BEOL所有的互连要求。因此,需要根据各个金属层的功能,选择不同的金属互连工艺来实现芯片性能。

三、芯片封装清洗剂选择:

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)