因为专业

所以领先

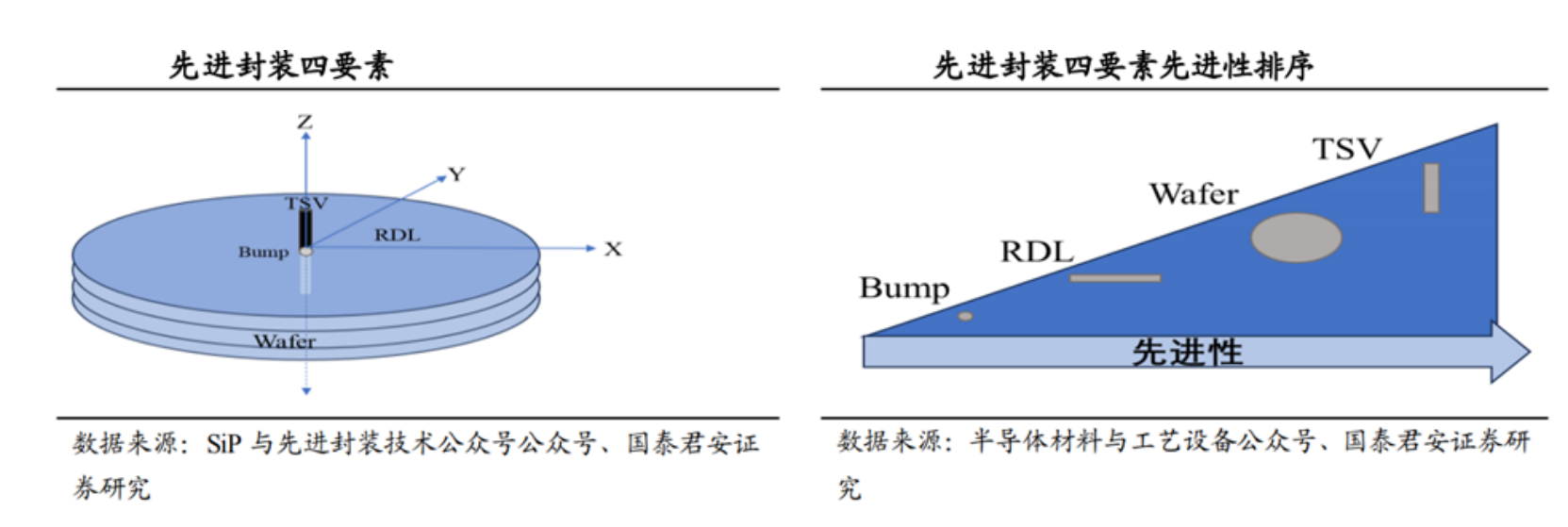

Bumping、RDL、Wafer和TSV是先进封装的四要素,具备其中一种即为先进封装。先进封装内涵丰富,相对传统封装,新增的底层工艺包括Bump(凸块),RDL(再布线层),Wafer(晶圆),TSV(硅通孔)四要素。Bump用来取代传统封装中的引线键合,主要起界面电气互联和应力缓冲的作用,当前先进封装无一例外均使用了Bump工艺。RDL起着XY平面电气延伸的作用,Interposer(中介层,以硅为主)也发挥相似作用,主要应用于晶圆级封装和2.5D/3D封装等技术。Wafer作为集成电路的载体以及RDL和TSV的介质和载体,在2.5D封装中用于制作硅基板、在WLP晶圆级封装中用于承载晶圆。TSV起着Z轴电气延伸的作用,是2.5D/3D封装技术实现的主要途径。从技术推出时间前后及先进性程度来看,排序为Bump、RDL、Wafer、TSV。

一、Bump(凸块)

该技术使用凸点(bump)代替传统引线,能够增加I/O触点密度,缩短传输距离。不同于要求焊盘分布于芯片四周的引线键合技术,面分布的凸点阵列允许I/O触点分布于芯片中间,大幅提高空间利用率和触点密度;利用倒装技术(FlipClip)和凸点垂直连接各芯片,也比引线键合的电路距离更短。

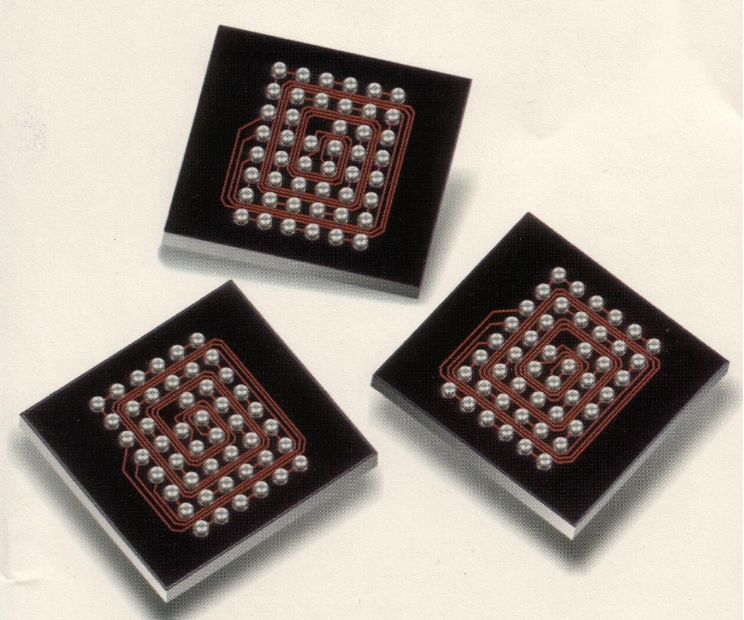

凸块技术主要分为球栅阵列焊球(Ball-Grid-Array Solder Ball,BGAball,直径0.25-0.76mm);倒装凸点(Flip-Chip Solder Bump,FCBump),也被称为可控塌陷芯片焊点(Controlled Callapse Chip Connection solder joint,C4solderjoint,直径100-150μm);微凸点(microbump,直径可小至2μm)。连接凸点时通常利用热压键合技术(Thermal Compressive Bonding)熔化焊球并使之冷却融合,并填入底部填充剂提高芯片机械性质。如今,微凸块的直径和间距仍在不断缩小。

混合键合技术(Hybrid Bonding)能够解决接点间距(Pitch)缩小时出现的问题,进一步提升接点密度、提升连接效率。当接点间距微缩至10微米左右时,焊锡球尺寸过小,容易在加热熔化过程中完全反应变质,降低导电性能;植球回流过程中两相邻焊锡球容易碰触在一起,导致芯片失效。混合键合技术通过将芯片或晶圆平面上抛光后凹陷的CuBump进行退火处理,使得Cu略微膨胀,两平面完全贴合,以无凸点(Bumpless)的方式缩减连接距离、提升接点密度、散热能力、信号传输准确度,从而降低能耗、提升效率。相比微凸点,混合键合技术能使I/O引脚密度增加5-10倍。当下,混合键合技术主要用于晶圆级封装,在晶圆制造环节即设计铜触点连接两片晶圆,切割后成为一体化的封装模块。

台积电、三星、英特尔领衔发展混合键合技术。当前,台积电的SoIC技术、三星的X-Cube技术、英特尔的FoverosDirect技术均运用了铜对铜直接键合的方式。使用SoIC的AMD锐龙75800X3D游戏台式处理器和锐龙7000X3D卓越游戏处理器率先实现量产。

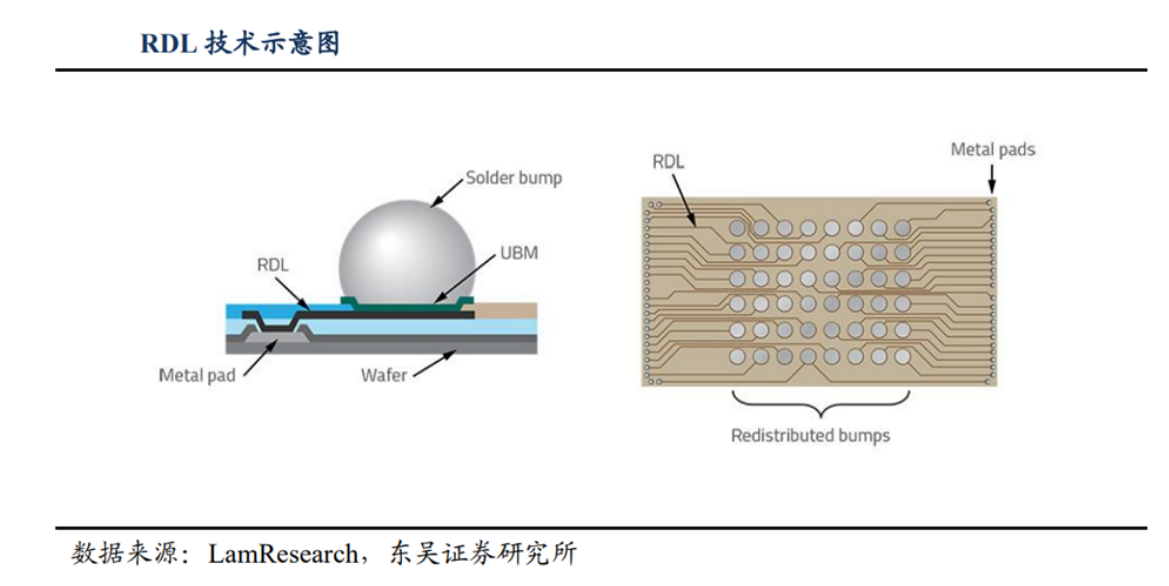

二、RDL(再布线层)

重布线层技术(RDL)。芯片的I/O触点通常分布在边缘或四周,直接进行封装会因缺少引线或引线过于密集而导致连接受限。RDL技术能够将裸片的触点重新布局到空间较为宽松的芯片中间,并使得接口处凸点面积更大、数量更多。当下的RDL技术能够将线距缩小至1-10μm的范围。

RDL技术使芯片在封装后支持更多的引脚,以增加芯片的算力、芯片间的连接。该优势广泛体现在晶圆级封装(Wafer Level Package)中。晶圆级封装主要分为扇入型晶圆级封装(Fan-inWLP)和扇出型晶圆级封装(Fan-outWLP),扇入型晶圆级封装利用RDL在芯片原有区域增加了触点,扇出型晶圆级封装则使用环氧塑封材料适当拓展芯片面积,同时利用RDL进行触点的二维延伸。

RDL技术能够代替中介层,从而缩小连接距离,提升传输速率。该技术能够在垂直堆叠封装时直接连接芯片和基板,为封装系统缩小减薄,提高集成度。台积电的InFO(Integrated Fan-out)系列封装技术即体现了该优势。与传统的垂直堆叠先进封装技术(如PoP等)不同,InFO没有使用硅中介层,而是在最底层逻辑芯片上进行了扇出塑封,并利用RDL技术在塑封区域布局上下连通的电路,以连接上层芯片和基板。该连接方式被称为TIV(Through-InFO-Via)。InFO首用于iPhone7,并助力台积电收获苹果A10芯片的全部订单。

三、Wafer(晶圆)

晶圆是芯片工艺实现的载体,用途广泛,逐渐向更大尺寸发展。晶圆是集成电路的载体,在晶圆上可以进行光刻、刻蚀、气相沉积、离子注入、研磨等多种处理工序,最终制成集成电路芯片。早先晶圆尺寸为6英寸到8英寸,现在普遍应用为12英寸,未来将广泛应用18英寸,晶圆正在向更大尺寸发展。随着晶圆的尺寸变大,先进封装技术更先进,晶圆用途也更加广泛,可以作为芯片的制作基底,也可以在晶圆上制作硅基板实现2.5D封装,还可以在晶圆级封装中承载晶圆。与传统封装是先切割晶圆再各自封装不同的是,晶圆级封装是先对整片晶圆进行封装再切割成小的芯片颗粒,封装面积与裸片一致,可以提高封装效率并降低封装成本。同时,晶圆级封装没有引线、键合和塑胶工艺,连接线路较短,可运用数组式连接,具有封装尺寸小、高传输速度、高密度连接、生产周期短等优点。

四、TSV(硅通孔)技术

为了缩小传输距离,人们使用堆叠芯片的方式进行封装。硅通孔技术通过将芯片的焊点打穿,并在通孔里填充金属材料(主要为铜),使芯片与芯片、芯片与基板实现垂直互连。比起传统的平铺芯片或者引线互连堆叠芯片,利用TSV的先进封装能够大幅缩小连接距离、提升连接效率。

硅通孔技术是实现2.5D及3D封装的关键解决方案。台积电的CoWoS封装中采用了大量TSV技术,其传输的高速和可靠性使之成为了AI(如英伟达A100、H100,AMDMI300)等高性能芯片的主流选择。

五、先进封装清洗剂介绍

芯片级封装在nm级间距进行焊接,助焊剂作用后留下的活性剂等吸湿性物质,较小的层间距如存有少量的吸湿性活性剂足以占据相对较大的芯片空间,影响芯片可靠性。要将有限的空间里将残留物带离清除,清洗剂需要具备较低的表面张力渗入层间芯片,达到将残留带离的目的。

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

是一家电子水基清洗剂 环保清洗剂生产厂家,其产品覆盖先进封装清洗剂、半导体清洗、芯片清洗、PCBA电路板清洗剂、助焊剂清洗剂等电子加工过程整个领域。 先进封装清洗剂产品包含晶圆级封装清洗剂、SIP系统级封装清洗剂、倒装芯片清洗剂、POP堆叠芯片清洗剂等。

推荐使用 水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)