因为专业

所以领先

当今的 SoC 需要多样化的功能和工作负载处理性能,因此很难将它们集成到单个芯片中。许多半导体制造公司也用单片硅生产大型产品,但这些产品通常是在尖端工艺节点制造的,因此成本高昂。

另一方面,如果将它们分开,仅靠传统的封装技术将无法成功地将它们商业化。英特尔之所以能够将 PCH 封装在 CPU 内部,是因为它通过传统封装设计了解散热、带宽、功率要求和硅成本。

先进封装是从SoC概念中增加集成度向在封装上配置系统的转变,是与延续摩尔定律的小型化+单片硅不同的做法。

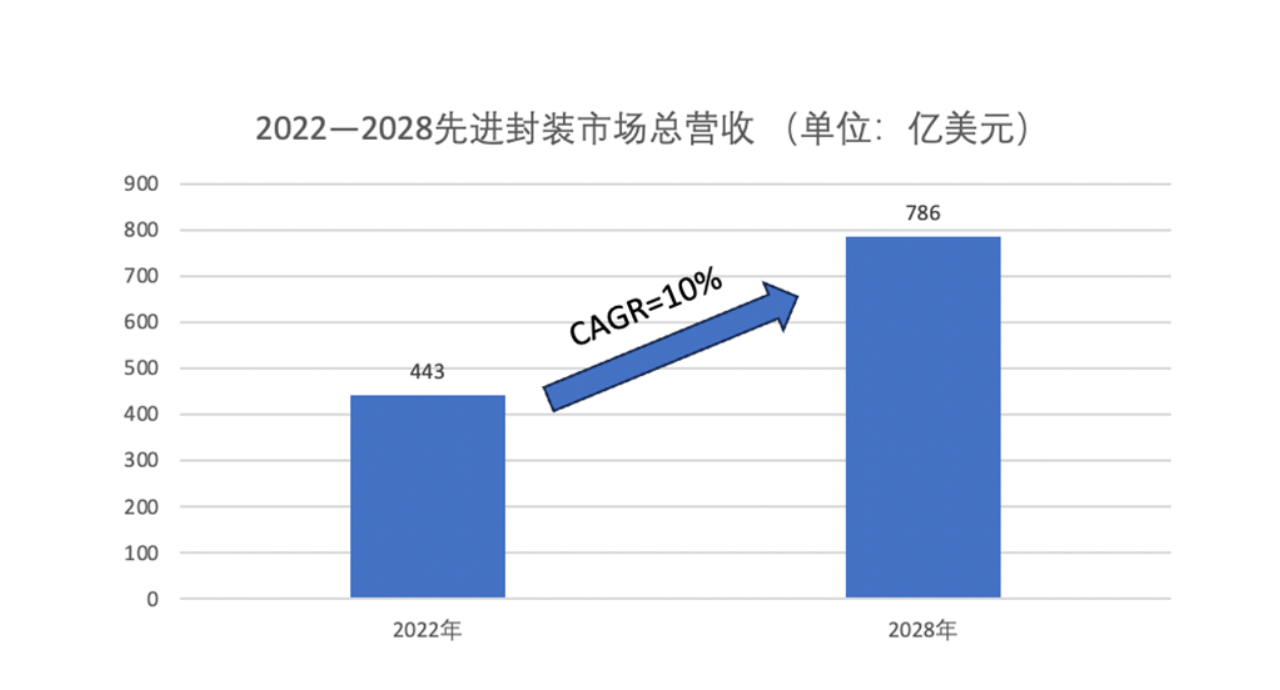

随着传统芯片制造愈发趋近于物理极限,先进封装市场增量越来越大。市场调研机构Yole数据显示,2022 年先进封装的市场总营收预计为443 亿美元,预计到 2028 年将达 786 亿美元,复合年均增长率将达到 10%。此外,先进封装的市场比重将逐渐超越传统封装,成为封测市场贡献主要增量。

其次,先进封装不仅市场增量越来越大,“花样”也越来越多。如今,这个传统上属于OSAT和IDM的领域,开始涌入来自不同商业模式的玩家,包括代工厂、设计厂商、基板/PCB供应商、EMS等企业均在进入先进封装市场。例如,晶圆级封装(WLP)技术如今主要由晶圆制造厂主导,2.5D/3D封装技术则主要由封测企业和设计企业主导,基板/PCB供应商在面板级封装(PLP)中起到关键作用。富士康和捷普等EMS厂商也在大力研发SiP等先进封装技术。全产业链上下游企业齐头涌入,恰恰说明了先进封装技术的不可或缺。

一、先进封装技术概述

先进封装技术的概念很广,包含了多种技术,倒装(FlipChip),凸块(Bumping),晶圆级封装(Waferlevelpackge),2.5D封装(interposer,RDL),3D封装(TSV)等都属于先进封装技术,这些技术的联合使用使得芯片的性能在晶体管尺寸不改变的前提下有了显著的提升。各封测厂商也推出了自己的封装技术平台,如台积电的InFO、CoWoS,日月光的FoCoS,Amkor的SLIM、SWIFT等。

FlipChip和Bumping是最早出现的先进封装技术,也是后续一系列技术的基础。FlipChip将芯片有源区面对着基板,通过芯片上呈阵列排列的Bumping实现芯片与衬底的互连,这使得互连长度大大缩短,减小了RC延迟,有效的提高了电性能。

RDL(再分布层)是将Die的引脚进行重新连接与分布,使连线路径重新规划,落到我们希望的区域,同时也可以获得更高的触点密度。

Interposer (中介层)指的是焊锡球和晶粒之间导电层。它的作用是扩大连接面,使一个连接改线到我们想要的地方。与再分布层作用类似。

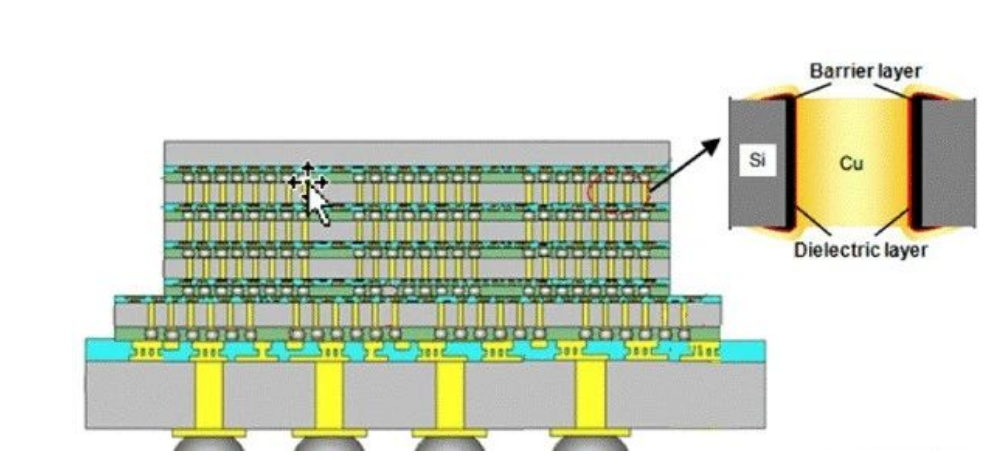

TSV(硅通孔)使得可以将芯片堆叠使三维空间被利用起来。不同的Die上下堆叠在一起,TSV实现上下层Die的通信,并且TSV是上下层芯片的最短通信路径。

无论是2.5D封装(interposer,RDL)还是3D封装(TSV),其目的都在于缩短信号传输距离,提高信号传输速度。

先进封装是“超越摩尔”(More than Moore)时代的一大技术亮点。当芯片在每个工艺节点上的微缩越来越困难、也越来越昂贵之际,工程师们将多个芯片放入先进的封装中,就不必再费力缩小芯片了。本文将对先进封装技术中最常见的10个术语进行简单介绍。

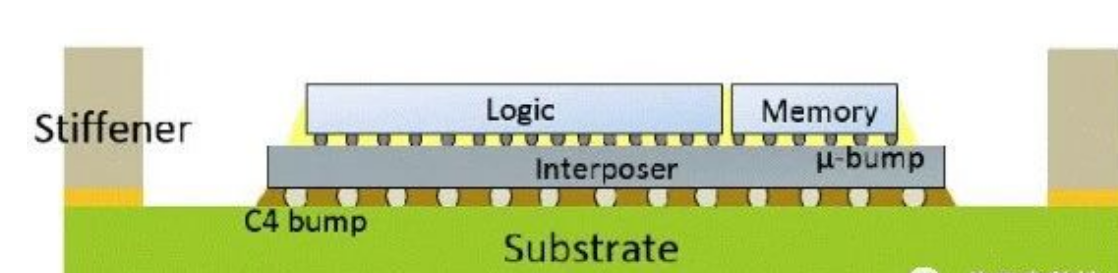

2.5D封装是传统2D IC封装技术的进展,可实现更精细的线路与空间利用。在2.5D封装中,裸晶堆栈或并排放置在具有硅通孔(TSV)的中介层(interposer)顶部。其底座,即中介层,可提供芯片之间的连接性。

2.5D封装通常用于高端ASIC、FPGA、GPU和内存立方体。将其大型FPGA划分为四个良率更高的较小芯片,并将这些芯片连接到硅中介层。2.5D封装由此诞生,并最终广泛用于高带宽内存(HBM)处理器整合。

▲2.5D封装示意图

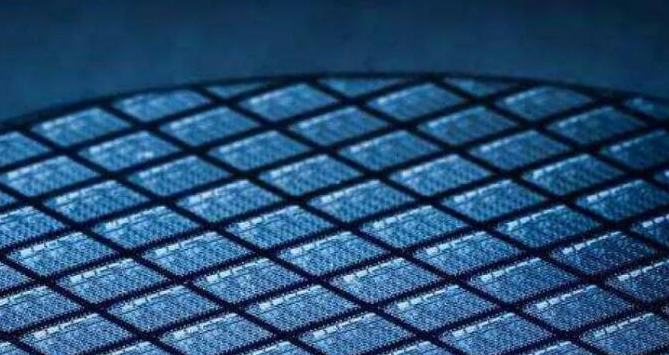

TSV技术是2.5D和3D IC封装中的关键使能技术,半导体产业一直使用HBM技术生产3D IC封装的DRAM芯片。

▲从3D封装的截面图可以看出,透过金属铜TSV实现了硅芯片之间的垂直互连

▲从3D封装的截面图可以看出,透过金属铜TSV实现了硅芯片之间的垂直互连

将大型SoC分解为较小的小芯片,与单颗裸晶相比具有更高的良率和更低的成本。Chiplet使设计人员可以充分利用各种IP,而不用考虑采用何种工艺节点,以及采用何种技术制造。他们可以采用多种材料,包括硅、玻璃和层压板来制造芯片。

与其他封装类型相比,扇出技术提供了具有更多 I/O 的小尺寸封装。

FOWLP技术是针对晶圆级封装(WLP)的改进,可以为硅芯片提供更多外部连接。它将芯片嵌入环氧树脂成型材料中,然后在晶圆表面建构高密度重分布层(RDL)并施加焊锡球,形成重构晶圆(reconstituted wafer)。

它通常先将经过处理的晶圆切成单颗裸晶,然后将裸晶分散放置在载体结构(carrier structure)上,并填充间隙以形成重构晶圆。FOWLP在封装和应用电路板之间提供了大量连接,而且由于基板比裸晶要大,裸晶的间距实际上更宽松。

七、芯片封装清洗:

研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用 水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)