基于 TSV 及 RDL 的异质集成方案简介( 堆叠封装PoP清洗)

基于 TSV 及 RDL 的异质集成方案

来源:半导体封装工程师之家

经过多年发展,TSV 封装技术的发展经历了从 TSV 简单互连、2.5D TSV 转接板、微凸点 3D 集成到 目前最为关注的无凸点 3D 集成。从应用的角度看,已 进入量产的基于 TSV 的封装技术主要集中在高端可 编程器件、图像处理器、存储芯片以及传感器芯片等 领域。

1、 基于 TSV 及 RDL 互连的晶圆级封装 :

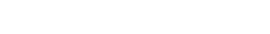

用 TSV 简单互连代替引线键合,实现硅背面与正 面有源区或金属布线之间的电气导通,是 TSV 在批量 生产中的首次使用。其典型应用包括图像、指纹、滤波 器、加速度计在内的传感器的封装,基于 TSV 的 MEMS 传感器封装结构如图 2 所示。使用 TSV 可减 小传感器模块的封装尺寸,利于进行晶圆级封装,提 高生产效率并降低成本。近年来发展出的基于后通孔 TSV 的埋入硅基三维异质集成技术,提供了 1 种低成 本、高性能的异质集成方案。2016 年,华天科技有限公 司开发出硅基埋入扇出(eSiFO)技术,使用硅片作为 载体,将芯片置于在 12 英寸硅晶圆上制作的高精度凹 槽内,重构出 1 个晶圆;然后采用可光刻聚合物材料填 充芯片和晶圆之间的间隙,在芯片和硅片表面形成扇 出的钝化平面;再通过光刻打开钝化层开口,并采用 晶圆级工艺进行布线和互连封装。硅基埋入封装具有 超小的封装尺寸、工艺简单、易于进行系统封装和高 密度三维集成等优点。同时,可通过制备背面 RDL 和 Via-last TSV,实现异质集成多芯片的三维堆叠封 装。其基本工艺流程包括:将测试正常的芯片嵌入单 个 eSiFO 封装体,然后分别在 eSiFO 封装体的正面和 背面形成 RDL,再通过微凸点和 Via-last TSV 实现多 个独立的 eSiFO 封装体与嵌入式芯片之间的电信号 互连。eSiFO 技术可以将由不同设计公司、晶圆厂设计 制造的各种晶圆尺寸和特征尺寸的不同系统或不同 功能的芯片集成到 1 个芯片中,从而实现真正的不同 封装体之间的三维异质集成封装。

2 、2.5D TSV 转接板异质集成 :

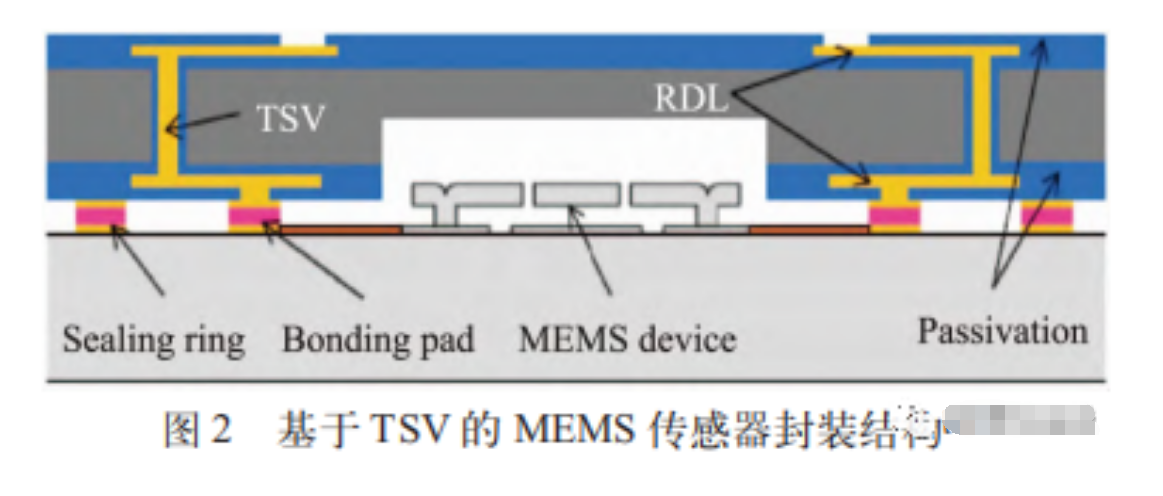

2.5D TSV 转接板技术是为解决有机基板布线密 度不足、信号延迟大、带宽限制等问题而开发的带有 TSV 垂直互连通孔和高密度金属布线的新型基板技 术。通过带有 TSV 垂直互连通孔的无源或有源载板,实现多个芯片间的高密度连接,再与有机基板互连以 提高系统集成密度,解决芯片管脚密度与有机基板引 出结构无法兼容的问题。典型 2.5D TSV 转接板异质 集成结构如图 3所示,采用 TSV 及微凸点(包括可 控塌陷 C4 凸点和铜柱 C2 凸点)实现垂直互连,通过 高密度 RDL 实现水平互连,实现中央处理器(CPU)、 图形处理器(GPU)、高带宽内存(HBM)等 Chiplet 的 异质集成。

IMEC、Fraunhofer、Leti、IME、台积电、联电等半导 体顶尖研究机构和企业均陆续推出各自的 2.5D TSV 转接板异质集成方案。其中,台积电于 2011 年推出的 2.5D 封装衬底上晶圆级芯片封装(CoWoS)技术最具 代表性,并成功实现大规模量产。该技术通过芯片到 晶圆工艺将芯片连接至硅转接板上,再把堆叠芯片与 基板连接,实现芯片-转接板-基板的三维封装结 构。该技术采用前道工艺在转接板上制作高密度的互 连线,通过转接板完成多个芯片的互连,可以大幅提 高系统集成密度,降低封装厚度。基于台积电的 CoWoS 技术,Xilinx 推出“Virtex-7 2000T”产品,该产 品将 4 个采用 28 nm 工 艺的现场可编程 门 阵 列 (FPGA) 芯片通过 TSV 转接板互连,实现了在单个 FPGA 模组里集成数个 FPGA 的功能,超越了摩尔定 律的限制[31]。此后推出的基于 CoWoS 技术的产品包括 华为海思 Hi616、英伟达 TESLA 显卡和 Fujistu A64FX 超级计算芯片等。针对高性能计算应用,台积电于 2020 年进一步开发了集成深沟槽电容 (DTC)的 CoWoS 技术,其电容密度高达 300 nF/mm2 ,漏电流小 于 1 fA/μm2 ,该 CoWoS 具有更低的功耗和更好的数 据传输性能。到 2021 年,CoWoS 技术已经发展至第 五代,转接板面积可达 2 500 mm2 ,单个转接板可集 成 8 个 HBM 和超过 3 个芯片级系统(SoC)/Chiplet 模 块;同时集成 DTC 以增强电源完整性,并发展出相应 的 5 层亚微米尺度的铜 RDL 互连技术。近年来,人工 智能、高性能计算等对超强算力的需求迅猛增长,大 力推动了 2.5D TSV 转接板封装技术的应用。通过异 质集成 CPU、GPU 和 HBM 获得更高的带宽密度,成 为提高算力的关键途径。根据对 TOP500 超级计算机 系统的分析,2020 年基于 CoWoS 技术的总计算能力 占所有 TOP500 系统总计算能力的 50%以上。

3、 基于 TSV 和微凸点的三维异质集成 :

3D 集成将芯片在垂直方向通过 TSV 和微凸点进 行堆叠,可以实现高性能、低功耗、高宽带、小形状因 子等目的,充分发挥晶圆级堆叠和 TSV 技术互连线长 度短的优势。该技术早期主要应用于动态随机存取存 储器(DRAM)、高带宽内存等。典型产品如 2014 年三 星基于 TSV 和微凸点互连量产的 64 GB DRAM,互连 TSV 尺寸为 7 μm×50 μm;与采用引线键合的内存相 比,信号传送速率提升一倍,而功耗减少一半。

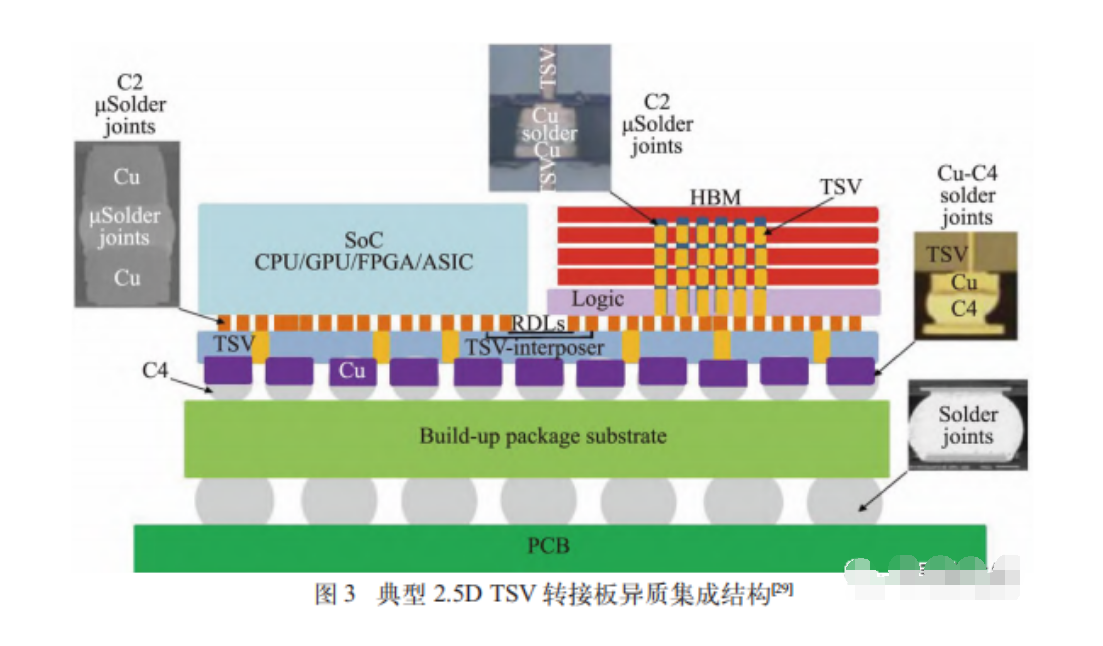

近年来,基于 TSV 和微凸点的三维集成技术不断 拓展到逻辑芯片的三维堆叠集成。2019 年,英特尔推 出基于 TSV 和微凸点的新型 3D 集成技术 Foveros,该 技术能够实现逻辑芯片的面对面堆叠,首次将芯片堆 叠从传统的无源中介层和内存等扩展到高性能逻辑 芯片,例如 CPU、GPU 和 AI 处理器等。10 nm 节 点工艺的计算芯片与 22 nm 节点工艺的有源芯片 3D Foveros 堆叠集成结构如图 4 所示。采用 Foveros 封 装技术的英特尔 Lakefield 处理器于 2020 年投入市场。三星也于 2020 年发布了X-Cube 三维集成技术,利用 TSV 和微凸点技术将 HBM 芯片与逻辑芯片进行堆 叠,在速度、功率、效率方面实现显著飞跃。

4、 基于无凸点混合键合的三维异质集成 :

一直以来,3D 集成广泛采用 Sn 基钎料微凸点和 TSV 实现高效的垂直互连。然而,当间距减小到 20 μm 以内,热压键合过程中的细微倾斜将使钎料变形挤出 而发生桥连短路。同时,液-固反应形成的金属间化合 物(IMC)将占据凸点的大部分体积,使之转变为脆性 连接。并且,表面扩散及柯肯达尔孔洞等问题的影响 急剧增加,难以进一步缩减互连间距,微凸点的微型 化遭遇前所未有的瓶颈。基于 Cu/ 绝缘层混合键合的无凸点 3D 集成可实现:

(1)刚性互连,避免出现桥 连问题;

(2) 与集成电路后道工序及 TSV 铜互连相兼 容,无需底充胶;

(3)芯片堆叠中多次热压工艺无影响 (铜的熔点为 1 083 ℃);

(4) 无脆性相 IMC 形成;

(5) 优异的电、热、机械和抗电迁移性能。因此,无凸点 Cu/ 绝缘层混合键合在超细间距(小于 10 μm)芯片垂直互 连中的应用具有无可比拟的优势。

对于 Cu-Cu 直接键合及 Cu/ 绝缘层混合键合的 研究已持续了几十年,然而由于当时的市场需求有限 并且工艺难度过大,其一直未引起过多关注。直到 2015 年,索尼获得 Ziptronix 公司的混合键合技术授 权,首次推出了基于无凸点混合键合的高性能图像传 感器产品。半导体业界逐渐意识到混合键合将成为 突破微凸点微型化瓶颈的有效途径。此后英特尔、台 积电、华为、长江存储、IMEC、IME、Leti 等领先机构和 企业陆续对混合键合技术进行了深入研发。英特尔 推出了基于无凸点混合键合的 Foveros 三维集成技 术,但未披露过多细节。台积电则较为详细地公布了 其基于无凸点混合键合的三维异质集成技术,将之称 为集成片上系统(SoIC),其混合键合工艺温度与无铅焊料回流工艺温度相当。SoIC 集成采用超薄芯 片,以实现大深宽比和高密度的 TSV 互连。为此,台积 电提出并优化 2 条工艺路线:

(1)芯片-晶圆键合后再 背面露铜,首先将芯片面对面混合键合,随后对芯片 背面减薄,背面露铜后沉积绝缘层和 Cu 盘,再次与另 一芯片 Cu-Cu 键合并重复以上工艺,实现芯片堆叠;

(2)背面露铜后再进行芯片-芯片键合,首先将晶圆临 时键合于玻璃载板并进行背面减薄,背面露铜后沉积 绝缘层和 Cu 盘,晶圆与载板解键合后切割成单颗芯 片,单颗芯片再分别进行 Cu-Cu 键合以实现芯片堆 叠。基于混合键合的 SoIC 及其改进版本 SoIC+ 可以 获得超细间距和超高密度的互连。它比倒装芯片技术 具有更好的电气性能,插入损耗几乎为零,远远小于 2D 并排倒装芯片技术的插入损耗。与台积电采用的传 统微凸点 3D TSV 集成对比,无凸点 SoIC 集成的 12 层存储器在垂直方向上的尺寸下降高达 64%,带宽密 度则增加 28%,而能源消耗下降 19%。

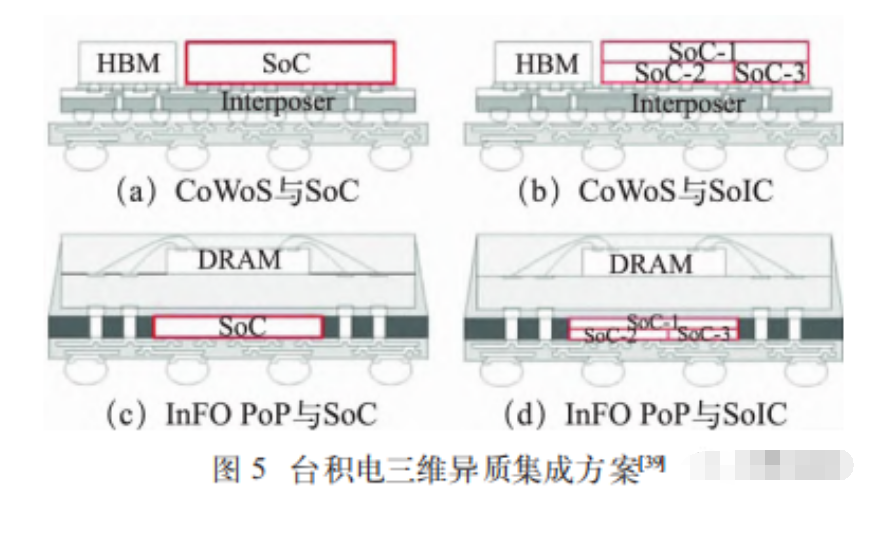

由此可见,无凸点 3D 集成技术可实现超高密度 的芯片垂直互连,继续推动芯片向高性能、微型化和 低功耗方向发展。同时,以台积电无凸点 3D 集成 SoIC 技术为例,SoIC 可与 CoWoS、集成扇出型封装等技术 实现深度异质集成整合,三维异质集成方案如图 5 所 示。原来需要放到 1 个片上系统 SoC 芯片上实现的 方案,现在可以转换成多个 Chiplet 来做。这些分解开 的 Chiplet 再通过集成 SoIC 实现灵活整合,其芯片产 品具有设计成本低、速度快、带宽足和低功耗的优势。因此,基于无凸点混合键合的三维异质集成技术若真 正实现量产,无疑是集成电路行业划时代的革新技 术。然而,当前该技术在设计规则、平整度、清洁度、材 料选择和对准等方面仍面临诸多挑战。

5、堆叠封装PoP清洗

PoP堆叠芯片清洗:PoP堆叠芯片/Sip系统级封装在mm级别间距进行焊接,助焊剂作用后留下的活性剂等吸湿性物质,较小的层间距如存有少量的吸湿性活性剂足以占据相对较大的芯片空间,影响芯片可靠性。要将有限的空间里将残留物带离清除,清洗剂需要具备较低的表面张力渗入层间芯片,达到将残留带离的目的。 研发的清洗剂具有卓越的渗入能力,以确保芯片间残留活性剂被彻底清除。

针对先进封装产品芯片焊后封装前,基板载板焊盘、电子制程精密焊后清洗的不同要求, 在水基清洗方面有比较丰富的经验,对于有着低表面张力、低离子残留、配合不同清洗工艺使用的情况,自主开发了较为完整的水基系列产品,精细化对应涵盖从半导体封装到PCBA组件终端,包括有水基清洗剂和半水基清洗剂,碱性水基清洗剂和中性水基清洗剂等。具体表现在,在同等的清洗力的情况下, 的兼容性较佳,兼容的材料更为广泛;在同等的兼容性下, 的清洗剂清洗的锡膏种类更多(测试过的锡膏品种有ALPHA、SMIC、INDIUM、SUPER-FLEX、URA、TONGFANG、JISSYU、HANDA、OFT、WTO等品牌;测试过的焊料合金包括SAC305、SAC307、6337、925等不同成分),清洗速度更快,离子残留低、干净度更好。

想了解更多关于先进封装产品芯片清洗的内容,请访问我们的“先进封装产品芯片清洗”产品与应用!

【阅读提示】

以上为本公司一些经验的累积,因工艺问题内容广泛,没有面面俱到,只对常见问题作分析,随着电子产业的不断更新换代,新的工艺问题也不断出现,本公司自成立以来不断的追求产品的创新,做到与时俱进,熟悉各种生产复杂工艺,能为各种客户提供全方位的工艺、设备、材料的清洗解决方案支持。

【免责声明】

1. 以上文章内容仅供读者参阅,具体操作应咨询技术工程师等;

2. 内容为作者个人观点, 并不代表本网站赞同其观点和对其真实性负责,本网站只提供参考并不构成投资及应用建议。本网站上部分文章为转载,并不用于商业目的,如有涉及侵权等,请及时告知我们,我们会尽快处理;

3. 除了“转载”之文章,本网站所刊原创内容之著作权属于

网站所有,未经本站之同意或授权,任何人不得以任何形式重制、转载、散布、引用、变更、播送或出版该内容之全部或局部,亦不得有其他任何违反本站著作权之行为。“转载”的文章若要转载,请先取得原文出处和作者的同意授权;

4. 本网站拥有对此声明的最终解释权。