什么是先进封装?

什么是先进封装?

传统封装需要将每个芯片都从晶圆中切割出来并放入模具中。晶圆级封装 (WLP) 则是先进封装技术的一种 , 是指直接封装仍在晶圆上的芯片。WLP 的流程是先封装测试,然后一次性将所有已成型的芯片从晶圆上分离出来。与传统封装相比,WLP 的优势在于更低的生产成本。

先进封装可划分为 2D 封装、2.5D 封装和 3D 封装。

更小的 2D 封装

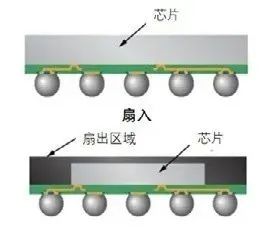

如前所述,封装工艺的主要用途包括将半导体芯片的信号发送到外部,而在晶圆上形成的凸块就是发送输入 / 输出信号的接触点。这些凸块分为扇入型 (fan-in) 和扇出型 (fan-out) 两种,前者的扇形在芯片内部,后者的扇形则要超出芯片范围。我们将输入/输出信号称为 I/O( 输入/输 出), 输入/输出数量称为 I/O 计数。I/O 计数是确定封装方法的重要依据。如果I/O计数低就采用扇入封装工艺。由于封装后芯片尺寸变化不大,因此这种过程又被称为芯片级封装(CSP)或晶圆级芯片尺寸封装(WLCSP)。如果 I/O 计数较高,则通常要采用扇出型封装工艺,且除凸块外还需要重布线层 (RDL) 才能实现信号发送。这就是“扇出型晶圆级封装 (FOWLP)”。

2.5D 封装

2.5D 封装技术可以将两种或更多类型的芯片放入单个封装,同时让信号横向传送,这样可以提升封装的尺寸和性能。最广泛使用的 2.5D封装方法是通过硅中介层将内存和逻辑芯片放入单个封装。2.5D 封装需要硅通孔 (TSV)、微型凸块和小间距 RDL 等核心技术。

3D 封装

3D 封装技术可以将两种或更多类型的芯片放入单个封装,同时让 信 号 纵 向 传 送。这 种 技 术 适 用于更小和 I/O 计数更高的半导体芯片。TSV 可用于 I/O 计数高的芯片,引线键合可用于 I/O 计数低的芯片,并最终形成芯片垂直排列的信号系统。3D 封装需要的核心技术包括 TSV 和微型凸块技术。

以上是关于先进封装基础知识介绍的相关内容,希望能您你有所帮助!

想要了解关于芯片半导体清洗的相关内容,请访问我们的“芯片半导体清洗”专题了解相关产品与应用 !

是一家电子水基清洗剂 环保清洗剂生产制造商,其产品覆盖电子加工过程整个领域。欢迎使用 水基清洗剂产品!

【阅读提示】

以上为本公司一些经验的累积,因工艺问题内容广泛,没有面面俱到,只对常见问题作分析,随着电子产业的不断更新换代,新的工艺问题也不断出现,本公司自成立以来不断的追求产品的创新,做到与时俱进,熟悉各种生产复杂工艺,能为各种客户提供全方位的工艺、设备、材料的清洗解决方案支持。

【免责声明】

1. 以上文章内容仅供读者参阅,具体操作应咨询技术工程师等;

2. 内容为作者个人观点, 并不代表本网站赞同其观点和对其真实性负责,本网站只提供参考并不构成投资及应用建议。本网站上部分文章为转载,并不用于商业目的,如有涉及侵权等,请及时告知我们,我们会尽快处理;

3. 除了“转载”之文章,本网站所刊原创内容之著作权属于

网站所有,未经本站之同意或授权,任何人不得以任何形式重制、转载、散布、引用、变更、播送或出版该内容之全部或局部,亦不得有其他任何违反本站著作权之行为。“转载”的文章若要转载,请先取得原文出处和作者的同意授权;

4. 本网站拥有对此声明的最终解释权。