SIP系统级封装工艺流程与技术

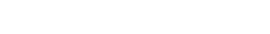

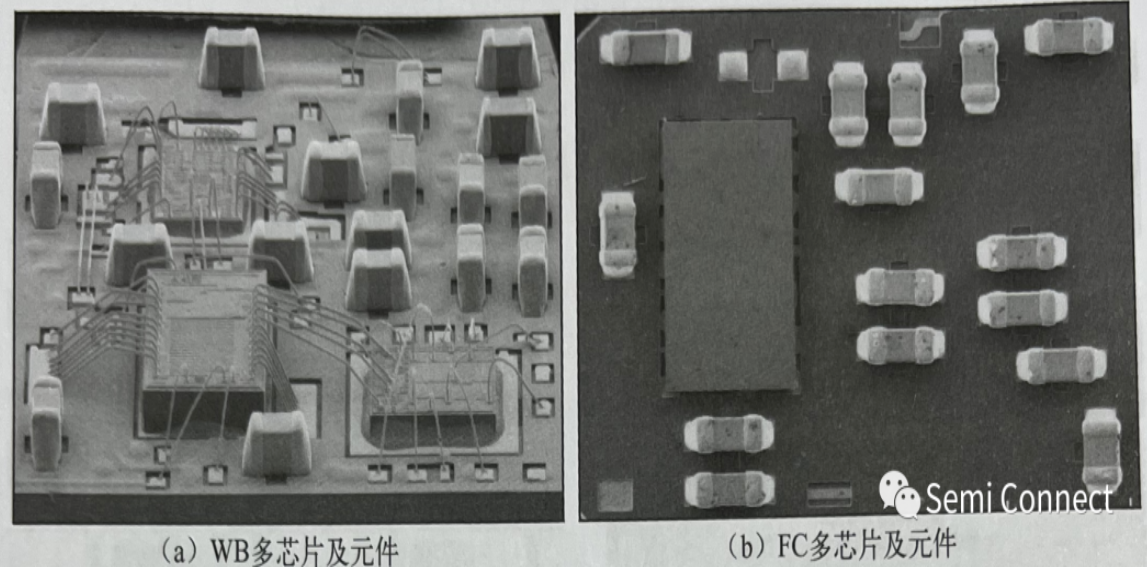

系统级封装 (System in Package, SiP)是指将单个或多个芯片与各类元件通过系统设计及特定的封装工艺集成于单一封装体或模块,从而实现具完整功能的电路集成,如图所示。与系统级芯片 (SoC)常用于集成数字及逻辑电路不同,系统级封装(SiP)更适用于无法(或非常困难)在单一芯片上实现功能集成的微波、射频、功率等模拟电路的应用。

作为一种通过封装工艺来实现集成电路产品的设计、开发和封测的主要技术和方法,SiP 并没有固定的封装形式和工艺,它可以在现有的大部分封装类型上实现。通常,SiP 因为产品功能多样化而选择相对灵活的 LGA 设计如图所示。但随着该技术在更大、更复杂的系统电路中的迅速推广,可以提供更多I/0 端口的 BGA 及整体化模块也逐渐得以广泛使用。另外,SiP 封装模块经常需要进行电磁屏蒰以消除模块电路与环境之间的交互影响,而电磁屏蔽通常可以利用简单的金属盖来实现。现在,高性能、高可靠性的 SiP 模块也越来越多地使用塑封料包封加金属涂层的工艺来实现电磁屏。

SiP 使用的基板和载体类型主要包括:薄膜厚膜及低温烧结陶瓷(LTCC)基板;高密度的引线框基板;单层、多层及埋人式的有机基板;扇出型圆片级无基板再布线(RDL)连按等。

SiP 的主要封装工艺方法和结构包括:多芯片SMT + WB/FC;芯片堆叠 SMT + WB/FC; 高密度3D/2.5D 封装;叠层封装(POP);扇出型圆片级SiP等。

SiP 典型工艺流程如图所示。由于 SiP涉及大量的多种类芯片和元器件,需要增加新的封装工艺,如 SMT、电磁屏蔽溅射涂层等。虽然主要的半导体封装工艺和设备可以共享,但 SP 工艺对这些通用封装工艺也有很多特殊的新要求。

(1)高密度小间距表面贴装:SiP 技术是推动元件及预封装芯片 (WICSP、超薄超小CSP)尺寸微型化的最大驱动力,0201、01005区更小尺寸 008004 的电感、电容都是首先在 SiP 模块中实现大批量使用的,先进的 WLCSP 的I/O间距小于 200μm,已接近 FC工艺。这些超小型元器件必须通过高速、高精度 SMT设备和工艺贴装于 SiP 基板上,并通过锡膏及锡焊回流工艺实现连接。锡膏由锡焊颗粒和助焊剂均匀混合而成,锡焊合金成分、颗粒尺寸分布及助焊剂类型的选择非常重要,通常应根据产品类型及工艺流程来确定。

(2)塑封:超小尺寸元器件及芯片,以区对应的高密度超小问距,有可能导致塑封料无法完全充分填充,从而造成可 靠性方面的隐患。通常的改善方法包括,优化塑封工艺参数,通过特殊的设计以增加塑封料的流动和填充,改变塑封料的固体颗粒的尺寸及分布,以及使用易于均匀填充的 Compresion 塑封工艺。

(3)电磁屏蔽金属涂层:如图所示,在塑封料表面形成电磁屏蔽金属涂层是通过等离子溅射工艺或直按电镀而实现的。因为工艺灵活,涂层结合力强,易于产能扩张,且不涉区湿法电化学所需要的废水处理,等离子溅射金属涂层已经逐步成为主流工艺。电磁屏蔽金属涂层一般由多层金属组成,从而保证金属涂层与塑封料表面形成牢固的结合力。主层金属常常选择纯铜,以利用其优异的导电性实现电磁干扰的屏蔽;外层金属可以选择不锈钢,从而确保封装体具有耐磨和良好的抗氧化性。为了形成完整的电磁屏蔽,金属涂层必领实现上表面及四侧面均覆盖并按地。对于更高、更复杂的系统级封装,也会使用分隔式电磁屏酸,从而进一步提高系统的整体电磁屏蔽效果。

【阅读提示】

以上为本公司一些经验的累积,因工艺问题内容广泛,没有面面俱到,只对常见问题作分析,随着电子产业的不断更新换代,新的工艺问题也不断出现,本公司自成立以来不断的追求产品的创新,做到与时俱进,熟悉各种生产复杂工艺,能为各种客户提供全方位的工艺、设备、材料的清洗解决方案支持。

【免责声明】

1. 以上文章内容仅供读者参阅,具体操作应咨询技术工程师等;

2. 内容为作者个人观点, 并不代表本网站赞同其观点和对其真实性负责,本网站只提供参考并不构成投资及应用建议。本网站上部分文章为转载,并不用于商业目的,如有涉及侵权等,请及时告知我们,我们会尽快处理;

3. 除了“转载”之文章,本网站所刊原创内容之著作权属于

网站所有,未经本站之同意或授权,任何人不得以任何形式重制、转载、散布、引用、变更、播送或出版该内容之全部或局部,亦不得有其他任何违反本站著作权之行为。“转载”的文章若要转载,请先取得原文出处和作者的同意授权;

4. 本网站拥有对此声明的最终解释权。