2. 5D 封装概述优点与先进封装清洗剂的应用

2. 5D 封装概述

什么是 2. 5D封装

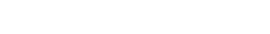

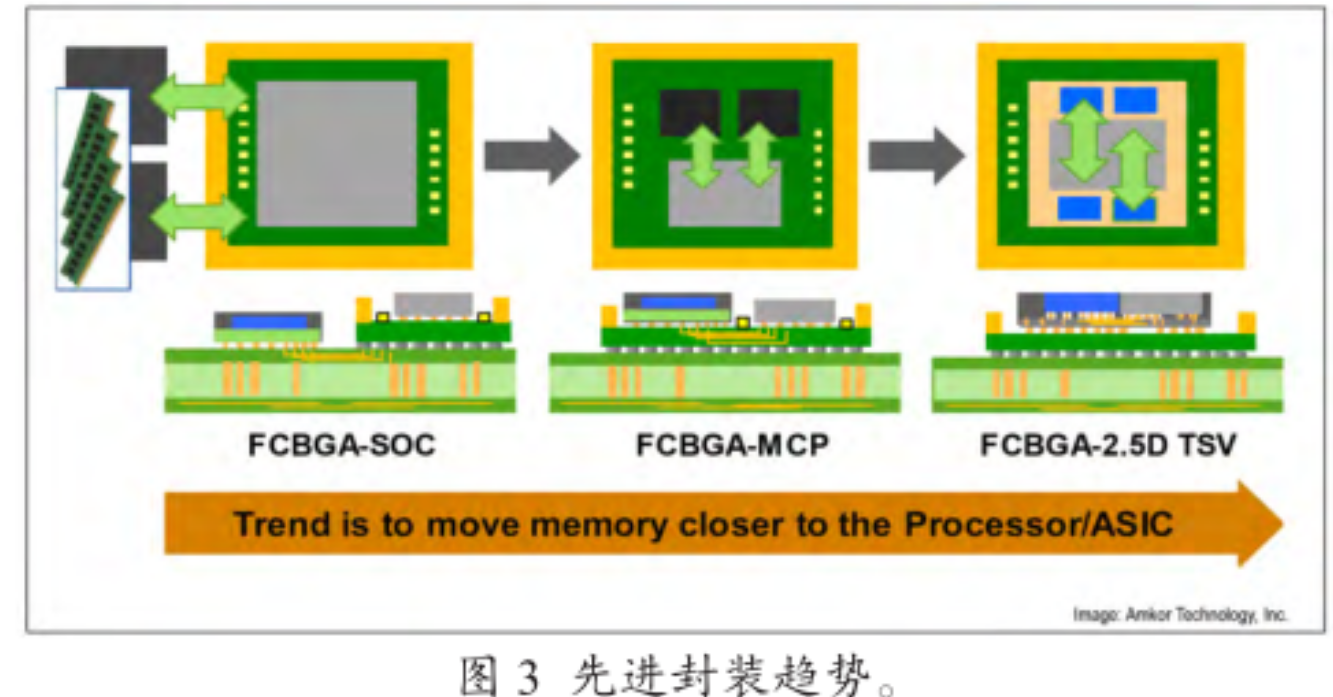

2.5D 封装是一种先进的异构芯片封装,能将多颗芯片做高密度的信号连接,集成进一个封装。它的主要特征包含三层立体种结构(如图 2 所示):

(1)主芯片等多颗芯片长微凸块后倒装;

(2)含硅通孔 (TSV) 的介质层(Si interposer)制

作凸块或锡球后,对应上下两层结构;

(3)将介质层倒装到基板上。

2. 5D 封装的优点

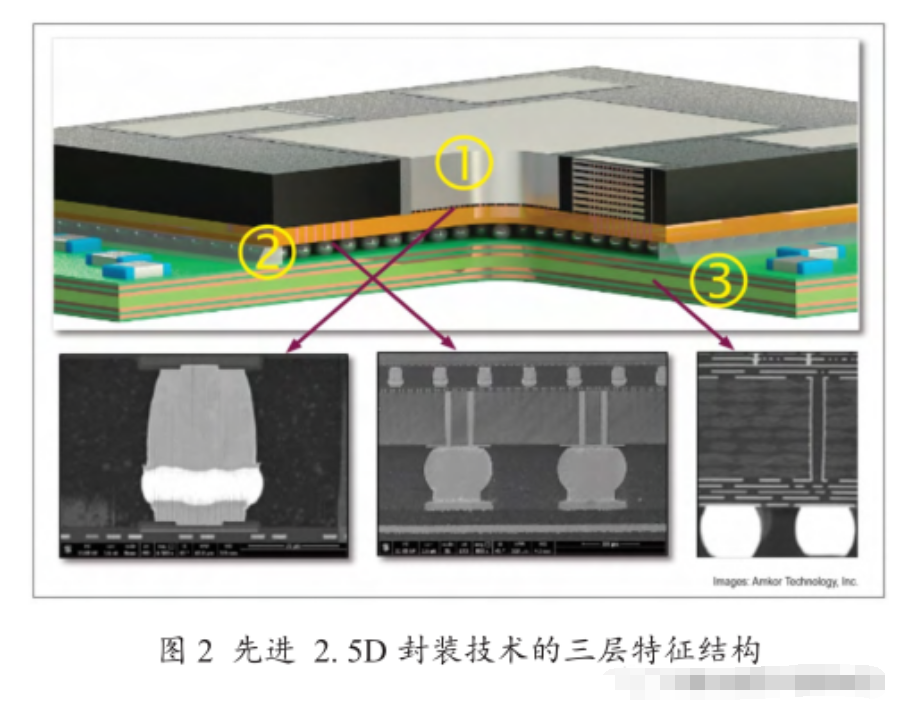

采用如此复杂的封装结构的原因有很多。如图3 所示,为了满足运算速度不断提升的需求,内存与主芯片的物理距离越趋靠近。从早期各自封装后, 通过系统板(PCB)对接,发展到 SiP, 将内存和主芯片通过基板 (Substrate) 对接形成 FCBGA 封装。进展到2.5D 的时代,内存提升到了新一代的 HBM,距离又拉得更近,通过硅介质层(Si Interposer)对接。主芯片和内存的距离演进从数十毫米缩小到数毫米再达到0.1 毫米(100μm)以下。距离的减小意味着时间延迟的缩短和电子信号质量的优化,可实现更高速度,而且降低能耗。

另一个原因是 HBM数据并行位宽有 1024 比特,这已不是 DDR4 或 GDDR5/GDDR5X/GDDR6 的16/32 比特所能相提并论。此外, HBM有大约 4,000个出球(输入 / 输出 / 电源 / 地),代表着与主芯片对接需要非常高的连接密度。传统的 FCBGA 基板线宽限制已无法满足这样的高密度连接要求,必须升级至 2.5D 硅介质层连接。

另一个重要趋势是 SerDes 的高速传输需求。单通路的 SerDes 发展达到每秒 10Gbps(千兆比特)、28Gbps、56 Gbps,甚至 112 Gbps 的速度。在高速数据中心应用中,主芯片控制着多个 SerDes 通路。随着制程节点的推进,在高性能要求、新 SerDes IP 确认完美匹配、上市时间压力等整体综效的考量下,市场朝着系统级芯片(SoC)设计的发展步伐并不一致。部分将采用 2.5D 异构芯片封装解决方案,将多颗SerDes 芯片与主芯片集成。

除此以外,还有一些是良率方面的考量。理论上来说,单个芯片的面积越大,良率越低。如 Bose-E-instein 良率模型:Y=1/ (1+AD)^k,Y 代表良率,A 代表芯片面积,D 代表缺陷密度,而 k 指的是难度层级系数。功能强大的高端芯片需要很大的芯片面积,预计良率也较低。因此, 在设计上将一个大芯片分解成多个较小的芯片,然后通过 2.5D 异构芯片封装,就能提高良率并且降低成本。这一点已经在 FPGA 中得到证明。

芯片封装基板的助焊剂清洗剂:

半导体芯片封装过程中通常会使用助焊剂和锡膏等作为焊接辅料,这些辅料在焊接过程或多或少都会有部分残留物,还包括制程中沾污的指印、汗液、角质和尘埃等污染物。同时,半导体组装了铝、铜、铂、镍等敏感金属和油墨字符、电磁碳膜和特殊标签等相当脆弱的功能材料。这些敏感金属和特殊功能材料对清洗剂的兼容性提出了很高的要求。

合明半水基清洗工艺解决方案,可在清洗芯片封装基板的焊接残留物和污垢的同时去除金属界面高温氧化膜,保障下一道工序的金属界面结合强度;对芯片半导体基材、金属材料拥有优良的材料兼容性,清洗后易于用水漂洗干净。

欢迎使用 半水基清洗剂W3300!

以上便是芯片封装基板清洗,封装基板的主要结构和生产技术的介绍,希望可以帮到您!

上一篇:第18届汽车电子产业链论坛彰显车用半导体行业协同创新

下一篇:Chip on Substrate(CoS)封装介绍与芯片封装清洗

【阅读提示】

以上为本公司一些经验的累积,因工艺问题内容广泛,没有面面俱到,只对常见问题作分析,随着电子产业的不断更新换代,新的工艺问题也不断出现,本公司自成立以来不断的追求产品的创新,做到与时俱进,熟悉各种生产复杂工艺,能为各种客户提供全方位的工艺、设备、材料的清洗解决方案支持。

【免责声明】

1. 以上文章内容仅供读者参阅,具体操作应咨询技术工程师等;

2. 内容为作者个人观点, 并不代表本网站赞同其观点和对其真实性负责,本网站只提供参考并不构成投资及应用建议。本网站上部分文章为转载,并不用于商业目的,如有涉及侵权等,请及时告知我们,我们会尽快处理;

3. 除了“转载”之文章,本网站所刊原创内容之著作权属于

网站所有,未经本站之同意或授权,任何人不得以任何形式重制、转载、散布、引用、变更、播送或出版该内容之全部或局部,亦不得有其他任何违反本站著作权之行为。“转载”的文章若要转载,请先取得原文出处和作者的同意授权;

4. 本网站拥有对此声明的最终解释权。